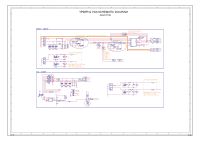

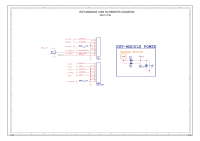

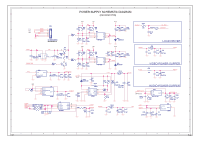

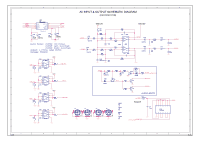

Toshiba 23HLV87 Circuit Diagrams - Page 23

Decoder Pcb

|

UPC - 022265000397

View all Toshiba 23HLV87 manuals

Add to My Manuals

Save this manual to your list of manuals |

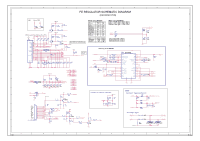

Page 23 highlights

8 7 6 5 4 3 2 1 H-29 A B C D E F G AV INPUT & OUTPUT SCHEMATIC DIAGRAM (DECODER PCB) AOUT0 ABCLK ALRCLK AMCLK U306 NM [CS4344/5/6] 1 2 3 4 5 SDIN SCLK LRCK MCLK VQ AOUTR VA GND AOUTL FILT+ 10 9 8 7 6 CS4344/5/6 C404 + NM [0.1uF] C328 NM [1uF/16V] C416 NM [0.1uF] A-RMAIN A5V A-LMAIN + C329 NM [1uF/16V] Audio format: CS4344: I2S format. CS4345: Left justified; CS4346: Right justified; Output: 1.17Vrms (when VA=5V) Package: TSSOP10 CVBS_C R72 75 R78 4 3 R70 510 510 D581 V+ 5 - 1 + V- 2 AD8061 VID5V R79 75 CVBS_OUT CVBS_G_Y R74 75 R80 4 3 R73 510 510 D420 V+ 5 - 1 + V- 2 AD8061 VID5V R81 75 GREEN C-B-U R63 75 R65 4 3 R62 510 510 D232 V+ 5 - 1 + V- 2 AD8061 VID5V R66 75 C-B-U_OUT Y-R-V R68 75 R76 4 3 R67 510 510 D239 V+ 5 - 1 + V- 2 AD8061 VID5V R77 75 Y-R-V_OUT H1 3 2 1 3 2 1 9 8 7 6 9 8 7 6 VID12V A-LMAIN C333 R27 1K 10uF/16V R25 10K R22 100K R19 5K1 + + C331 A-RMAIN R33 1K 10uF/16V R30 5K1 R28 100K + C332 100uF/16V R20 10K R21 3K9 C20 2.7n R31 3K9 C19 200P 2 V+ 8 - 1 R23 10K 3+ N306 R26 5 10K 6 4558 + 7 V- 4 C23 200P R32 10K C22 2.7n VID12V VID12V C335 + 10uF/16V C334 + 10uF/16V R35 100 R36 47K R38 100 R39 47K FB10 600 FB11 600 4 5 4 5 H2 3 2 1 3 2 1 H1 9 8 7 6 9 8 7 6 RAF5V R311 10K + C323 10uF/16v R318 000 R308 4K7 + C322 NC 2 3 Q303 1 601 D303 000 D303 ISS355 1 D301 ISS355 709 2 3 MUTE Q304 D3 R34 1 601 1K 2 3 3 D4 R37 1 601 1K R148 DUPRD1 4K7 MUTE_CTL AUDIO-R AUDIO-L 2 AUDIO-MUTE MARK1 FB17 5VOUT 601 5VOUT 11 10 9 8 1. 1. 1. 1. 9 8 7 6 4 5 4 5 H2 H3 3 2 1 3 2 1 9 8 7 6 4 5 4 5 H4 3 2 1 3 2 1 H3 9 8 7 6 4 5 4 5 H4 9 8 7 6 MARK2 MARK3 MARK4 S/PDIF_OUT S/PDIF_OUT C37 120P 7 6 5 U109 74HCU04 4 3 12 2 13 1 14 H AUDIO-R C24 330P AUDIO-L C25 330P COAX A B C D E F G H 8 7 6 5 4 3 2 1 H-30