Foxconn A74MX-S English manual - Page 39

► Memory Speed Mode, ► Memory Speed Adjust - k am2

|

View all Foxconn A74MX-S manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 39 highlights

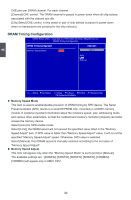

3 CKE pins per DRAM channel. For each channel : [Channel] CKE control. The DRAM channel is placed in power down when all chip selects associated with the channel are idle. [Chip Select] CKE control. A chip select or pair of chip selects is placed in power down when no transactions are pending for the chip select(s). DRAM Timing Configuration CMOS Setup Utility - Copyright (C) 1985-2006, American Megatrends, Inc. DRAM Timing Configuration D�R�A�M�T�im�in�g �Co�n�fig�ur�at�io�n H�elp�I�te�m Memory Speed Mode A�ut�o]]� Options Auto� Limit Manual Move Enter:Select +/-/:Value F10:Save ESC:Exit F1:General Help F9:Optimized Defaults ► Memory Speed Mode This item is used to enable/disable provision of DRAM timing by SPD device. The Serial Presence Detect (SPD) device is a small EEPROM chip, mounted on a DDR2 memory module. It contains important information about the module's speed, size, addressing mode and various other parameters, so that the motherboard memory controller (chipset) can better access the memory device. Select [Auto] for SPD enable mode. Select [Limit], the DRAM speed will not exceed the specified value listed in the "Memory Speed Adjust" item. If SPD value is faster than "Memory Speed Adjust" value, it will run at the specified "Memory Speed Adjust" speed. Otherwise, SPD value is selected. Select [Manual], then DRAM speed is manually selected according to the set value of "Memory Speed Adjust". ► Memory Speed Adjust This item will appear only when the "Memory Speed Mode" is set to [Limit] or [Manual]. The available settings are : [400MHz], [533MHz], [667MHz], [800MHz], [1066MHz]. [1066MHz] will appear only in AM2+ CPU. 32