HP Vectra VL800 hp vectra vl800, technical reference manual - desktop and mini - Page 55

Main Memory Controller

|

View all HP Vectra VL800 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 55 highlights

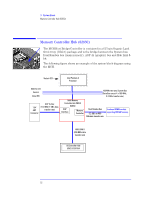

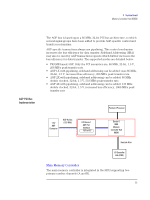

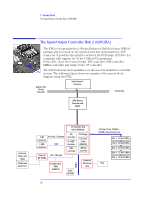

3 System Board Memory Controller Hub (82850) AGP PCI Bus Implementation The AGP bus is based upon a 66 MHz, 32-bit PCI bus architecture, to which several signal groups have been added to provide AGP-specific control and transfer mechanisms. AGP specific transactions always use pipelining. This control mechanism increases the bus efficiency for data transfer. Sideband Addressing (SBA) may also be used by AGP transaction requests which further increases the bus efficiency for data transfer. The supported modes are detailed below: • FRAME-based AGP. Only the PCI semantics are: 66 MHz, 32-bit, 1.5 V, 266 MB/s peak transfer rate. • AGP 1X with pipelining, sideband addressing can be added: uses 66 MHz, 32-bit, 1.5 V, increased bus efficiency, 266 MB/s peak transfer rate. • AGP 2X with pipelining, sideband addressing can be added: 66 MHz double clocked, 32-bit, 1.5 V, 533 MB/s peak transfer rate. • AGP 4X with pipelining, sideband addressing can be added: 133 MHz double clocked, 32-bit, 1.5 V, increased bus efficiency, 1066 MB/s peak transfer rate Pentium 4 Processor 1.5V AGP Connector AGP 4x Bus (133 MHz) GX-Device 1 AGP Port Interface PCI-to-PCI Device 0 I850 Memory Controller Hub (MCH) Hub Link 8-bit I/O Controller Hub (ICH2) Main Memory Controller The main memory controller is integrated in the MCH supporting two primary rambus channels (A and B). 55