Hitachi DK23EA Specifications - Page 39

Minimum PIO Transfer Cycle Time without Flow Controlns - - 60

|

View all Hitachi DK23EA manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 39 highlights

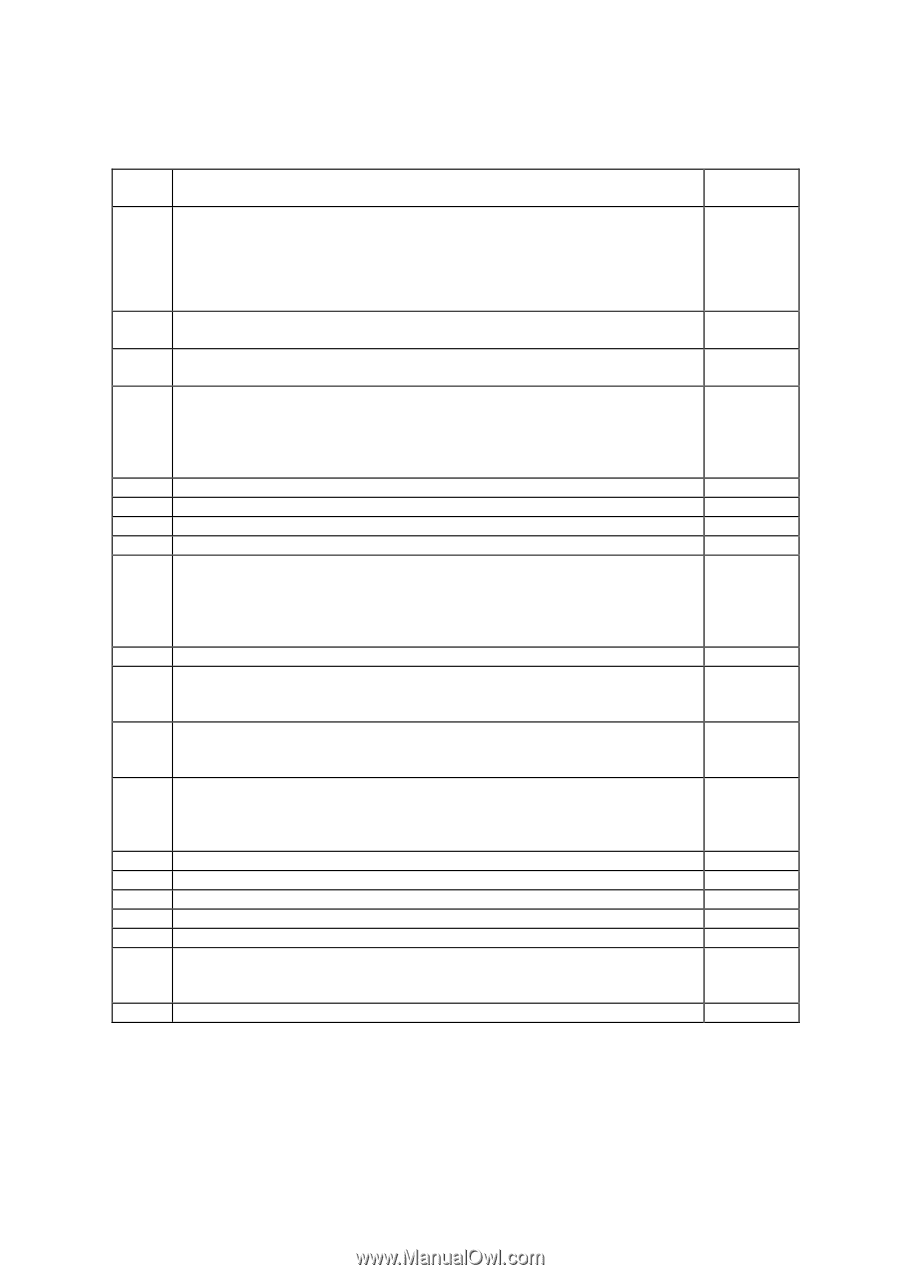

Word Table 6.5 Identify Device Information (Continued) Description 50 51 52 53 54 55 56 57-58 59 60-61 62 63 64 65 66 67 68 69-74 75 76-79 Capabilities Bit 15 0 (fixed) Bit 14 1 (fixed) Bit 13 - 1 0 = Reserved Bit 0 1 = Standby timer value is equal to or greater than 5 minutes. Reserved. Bit 15 - 8 PIO data transfer cycle timing mode Bit 7 - 0 Vendor Specific Bit 15 - 8 DMA data transfer cycle timing mode Bit 7 - 0 Vendor Specific Field validity Bit 15 - 3 0 = Reserved Bit 2 1 = The field reported in word 88 is valid Bit 1 1 = The fields reported words 64-70 are valid Bit 0 1 = The fields reported words 54-58 are valid Number of current cylinders Number of current heads Number of current sectors per track Current capacity in sectors Multiple sector setting Bit 15-90 = Reserved Bit 8 1 = Multiple sector setting is valid Bit 7 - 0Current setting for number of sectors that can be transferred per interrupt on R/W MULTIPLE command Total addressable LBA Single word DMA transfer Bit 15 - 8 Single word DMA transfer mode active Bit 7 - 0Single word DMA transfer mode supported Multi-word DMA transfer Bit 15 - 8 Multi-word DMA transfer mode active Bit 7 - 0Multi-word DMA transfer mode supported Flow control PIO transfer Modes supported Bit 15 - 2 0 = Reserved Bit 1 1 = PIO Mode 4 supported Bit 0 1 = PIO Mode 3 supported Minimum Multi-word DMA Transfer Cycle Time Per Word(ns) Manufacturer's Recommended Multi-word DMA Cycle Time(ns) Minimum PIO Transfer Cycle Time without Flow Control(ns) Minimum PIO Transfer Cycle Time with IORDY(ns) Reserved Queue Depth Bit 15 - 5 0 = Reserved Bit 4 - 0 Maximum queue depth Reserved Value (HEX.) 4000h 0200h 0200h 0007h See table 6.6 0003h 0078h 0078h 0190h 0078h 0000h 0000h 0000h K6602637 Rev.3 02.27.01 - 39 -