Intel E5310 Specification Update - Page 11

Errata Sheet 2 of 6 - processor number

|

UPC - 735858190800

View all Intel E5310 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 11 highlights

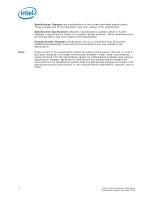

Errata (Sheet 2 of 6) Number Steppings B-3 G-0 AJ23 X AJ24 X X AJ25 X X AJ26 X X AJ27 X X AJ28 X X AJ29 X X AJ30 X AJ31 X AJ32 X X AJ33 X Status Plan Fix No Fix No Fix No Fix No Fix No Fix No Fix Plan Fix Plan Fix No Fix Plan Fix AJ34 X X No Fix AJ35 X AJ36 X AJ37 X X No Fix X No Fix Plan Fix AJ38 X Plan Fix AJ39 X AJ40 X AJ41 X AJ42 X AJ43 X AJ44 X AJ45 X AJ46 X Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix Plan Fix X No Fix X No Fix ERRATA VMCALL to Activate Dual-monitor Treatment of SMIs and SMM Ignores Reserved Bit settings in VM-exit Control Field The PECI Controller Resets to the Idle State Some Bus Performance Monitoring Events May Not Count Local Events under Certain Conditions Premature Execution of a Load Operation Prior to Exception Handler Invocation General Protection (#GP) Fault May Not Be Signaled on Data Segment Limit Violation above 4-G Limit EIP May be Incorrect after Shutdown in IA-32e Mode #GP Fault is Not Generated on Writing IA32_MISC_ENABLE [34] When Execute Disable Bit is Not Supported (E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast String REP STOS With Large Data Structures Performance Monitoring Events for Retired Loads (CBH) and Instructions Retired (C0H) May Not Be Accurate Upper 32 bits of 'From' Address Reported through BTMs or BTSs May be Incorrect Unsynchronized Cross-Modifying Code Operations Can Cause Unexpected Instruction Execution Results MSRs Actual Frequency Clock Count (IA32_APERF) or Maximum Frequency Clock Count (IA32_MPERF) May Contain Incorrect Data after a Machine Check Exception (MCE) Incorrect Address Computed For Last Byte of FXSAVE/FXRSTOR Image Leads to Partial Memory Update Split Locked Stores May not Trigger the Monitoring Hardware REP CMPS/SCAS Operations May Terminate Early in 64-bit Mode when RCX >= 0X100000000 FXSAVE/FXRSTOR Instructions which Store to the End of the Segment and Cause a Wrap to a Misaligned Base Address (Alignment