Intel E6600 Specification Update

Intel E6600 - Core 2 Duo Dual-Core Processor Manual

|

UPC - 735858184625

View all Intel E6600 manuals

Add to My Manuals

Save this manual to your list of manuals |

Intel E6600 manual content summary:

- Intel E6600 | Specification Update - Page 1

Intel® Core™2 Extreme Processor X6800Δ and Intel® Core™2 Duo Desktop Processor E6000Δ and E4000Δ Sequence Specification Update - on 65 nm Process in the 775-land LGA Package supporting Intel® 64Φ Architecture, Intel® Virtualization Technology± and Intel® Trusted Execution Technologyŧ December 2010 - Intel E6600 | Specification Update - Page 2

specifications and before placing your product order. Φ Intel® 64 requires a computer system with a processor, chipset, BIOS, operating system, device drivers, and applications enabled for Intel 64. Processor will not operate (including 32-bit operation) without an Intel 64-enabled BIOS. Performance - Intel E6600 | Specification Update - Page 3

of Changes 8 Identification Information ...17 Component Identification Information 20 Errata ...23 Specification Changes ...69 Specification Clarifications 70 Documentation Changes ...71 § Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence - Intel E6600 | Specification Update - Page 4

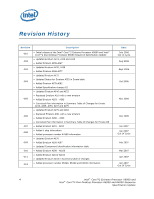

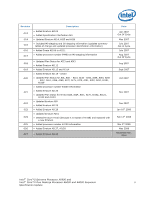

Revision History Revision -001 -002 -003 -004 -005 -006 -007 -008 -009 -010 -011 -012 Description • Initial release of the Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 Sequence Specification Update • Updated Erratum AI19, AI29 and AI40 • Added Erratum AI58- - Intel E6600 | Specification Update - Page 5

AI129 Date Apr 2007 Out Of Cycle May 2007 July 2007 Out of Cycle July 2007 Aug 2007 Out Of Cycle Aug 2007 Sept 2007 Oct 2007 Nov 2007 Dec 2007 Jan 16th 2008 Feb 13th 2008 Mar 3rd 2008 May 2008 December 8th, 2010 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 - Intel E6600 | Specification Update - Page 6

Intel® 64 and IA-32 Architectures Software Developer's Manual Volume 3B: System Programming Guide Document Location http://www.intel.com/product s/processor/manuals/index.h tm 6 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification - Intel E6600 | Specification Update - Page 7

documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.). § Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence - Intel E6600 | Specification Update - Page 8

fixed. There are no plans to fix this erratum. Row Shaded: This item is either new or modified from the previous version of the document. 8 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 9

= Dual-Core Intel® Xeon® processor 7000 sequence Intel® Celeron® processor Dual-Core Intel® Xeon® processor 2.80 GHz Intel® Pentium® III processor Intel® Pentium® processor Extreme Edition and Intel® Pentium® D processor Dual-Core Intel® Xeon® processor 5000 series 64-bit Intel® Xeon® processor MP - Intel E6600 | Specification Update - Page 10

Core™2 Duo Processor and Intel® Core™2 Extreme Processor on 45-nm Process Quad-Core Intel® Xeon® processor 3300 series Dual-Core Intel® Xeon® E3110 Processor Intel® Celeron® dual-core processor E1000 series Intel® Core™2 Extreme Processor QX9775Δ Intel® Atom™ processor Z5xx series The Specification - Intel E6600 | Specification Update - Page 11

RSM instruction Bit is Not Supported AI30 X X Fixed (E)CX May Get Incorrectly Updated When Performing Fast String REP MOVS or Fast String REP STOS With Large Data Structures Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 11 Specification - Intel E6600 | Specification Update - Page 12

in 64-bit Mode when RCX >= 0X100000000 AI38 X X X X Fixed FXSAVE/FXRSTOR Instructions Instruction if it is Followed by an Instruction That Signals a Floating Point Exception 12 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification - Intel E6600 | Specification Update - Page 13

Not be Indicated Unless IA32_DEBUGCTL[12] is Set AI73 X X X X X No Fix The BS Flag in DR6 May be Set for Non-Single-Step #DB Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 13 Specification Update - Intel E6600 | Specification Update - Page 14

X Fixed Performance Monitoring Counter MACRO_INSTS.DECODED May Not Count Some Decoded Instructions AI95 X X X X Fixed The Stack Size May be Incorrect as a Result of VIP/VIF Check on SYSEXIT and SYSRET 14 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and - Intel E6600 | Specification Update - Page 15

of-date LBR Instruction Fetch May Cause a Livelock During Snoops of the L1 Data Cache AI116 X X X X X No Fix Use of Memory Aliasing with Inconsistent Memory Type may Cause a System Hang or a Machine Check Exception Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor - Intel E6600 | Specification Update - Page 16

AI1 Clarification of TRANSLATION LOOKASIDE BUFFERS (TLBS) Invalidation Number DOCUMENTATION CHANGES - There are no Documentation Changes in this Specification Update revision. § 16 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence - Intel E6600 | Specification Update - Page 17

S/N Figure 2. Intel® Core™2 Duo Desktop Processor 2M SKU Package with 1066 MHz FSB INTEL M ©'05 INTEL® CORE™2 DUO 6400 SLxxx [COO] 2.13GHZ/2M/1066/06 [FPO] e4 ATPO S/N Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 17 Specification Update - Intel E6600 | Specification Update - Page 18

S/N Figure 4. Intel® Core™2 Duo Desktop Processor 4M SKU Package with 1333 MHz FSB INTEL M ©'05 E6850 INTEL® CORE™2 DUO SLxxx [COO] 3.00GHZ/4M/1333/06 [FPO] e4 ATPO S/N 18 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 19

Identification Information Figure 5. Intel® Core™2 Extreme Processor Package INTEL M ©'05 INTEL® CORE™2 EXTREME 6800 SLxxx [COO] 2.93GHZ/4M/1066/05B [FPO] e4 ATPO S/N § Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 19 Specification Update - Intel E6600 | Specification Update - Page 20

's Guide (BWG) for further information on the CPUID instruction. The following notes are applicable to Table 1 through Table 3. NOTES: 1. These processors support the 775_VR_CONFIG_06 specifications. 2. These processors support the 775_VR_CONFIG_05B specifications 3. These parts support Intel® 64 - Intel E6600 | Specification Update - Page 21

, 17 Table 2. Intel® Core™2 Duo Desktop Processor 4M SKU Identification Information S-Spec Core Stepping L2 Cache Size (bytes) Processor Signature Processor Number SLA4U B2 4M 06F6h E6320 SLA4T B2 4M 06F6h E6420 SL9S8 B2 4M 06F6h E6600 SL9ZL B2 4M 06F6h E6600 SL9S7 B2 4M - Intel E6600 | Specification Update - Page 22

) Processor Signature Processor Number SL9S5 B2 4M 06F6h X6800 Speed Core/Bus 2.93 GHz / 1066 MHz Package 775-land LGA Notes 2, 3, 4, 6, 7, 8, 9, 10, 11, 12, 13, 15 22 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification - Intel E6600 | Specification Update - Page 23

Machine-Check Architecture (MCA) on Single-bit L2 ECC Errors May be Incorrect Problem: When correctable Single-bit ECC errors occur in the L2 cache, -bit L2 ECC errors. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 23 Specification - Intel E6600 | Specification Update - Page 24

instruction can not be used if the RF flag needs to be set after returning from a system call. Intel has not observed this erratum with any commercially available software. 24 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification - Intel E6600 | Specification Update - Page 25

Protection Fault (#GP) for Instructions Greater than 15 Bytes May be Preempted Problem: When the processor encounters an instruction that is greater than 15 bytes Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 25 Specification Update - Intel E6600 | Specification Update - Page 26

APIC Register Sometimes May Appear to Have Not Occurred Problem: With respect to the retirement of instructions, stores to the uncacheable memory-based APIC register 26 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 27

instructions, if executed during HLT or MWAIT events, are also not counted: a) RSM from a C-state SMI during an MWAIT instruction. b) RSM from an SMI during a HLT instruction. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 27 Specification - Intel E6600 | Specification Update - Page 28

Issue Software which is written so that multiple agents can modify the same shared unaligned memory location at the same time may experience a memory 28 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 29

Problem: Code Segment limit violation may occur on 4 Gigabyte limit check when the code stream wraps around in a way that one instruction ends m32int • FISTTP m64int Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 29 Specification Update - Intel E6600 | Specification Update - Page 30

. Note that this is a "sticky" bit, i.e., once set by an inexact-result May have Nondeterministic Results Problem: If code sequentially executes instructions found there. 30 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification - Intel E6600 | Specification Update - Page 31

events are to be counted (local core, other core or both cores). Due to this erratum, some Bus Performance Monitoring events may not count when the core-specificity is set to the local core. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 31 - Intel E6600 | Specification Update - Page 32

occur above the 4G limit (0ffffffffh) may not signal a #GP fault. Implication: When such memory accesses occur in 32-bit mode, the system may not issue a #GP fault. 32 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 33

when multiplied by the data size give values larger than the address space size (64K for 16-bit address size and 4G for 32-bit address size). Status: For the steppings affected, see the Summary Tables of Changes. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 - Intel E6600 | Specification Update - Page 34

XMC to modify the instruction byte stream of a processor can see unexpected or unpredictable execution behavior from the processor that is executing the modified code. 34 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 35

following the MWAIT, when another logical processor performs a write access to a WB cacheable address within the address range used to perform the MONITOR operation. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 35 Specification Update - Intel E6600 | Specification Update - Page 36

May Terminate Early in 64-bit Mode when RCX >= 0X100000000 Problem: REP CMPS (Compare String) and SCAS (Scan String) instructions in 64-bit mode may terminate before . 36 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 37

was in compatibility mode • Bit 31 of the FPU Data (Operand) Pointer is set. • An FXSAVE instruction is executed Implication: Software depending on the full FPU Data (Operand) Pointer may behave unpredictably. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and - Intel E6600 | Specification Update - Page 38

-Bootstrap Processors Problem: When a logical processor encounters an error resulting in shutdown, nonbootstrap processors in the package may be unexpectedly disabled. 38 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 39

while servicing the original task switch then the VM bit will be incorrectly cleared in EFLAGS, data segments will not be pushed and the processor will not return to the correct mode upon completion of the second fault handler via IRET. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo - Intel E6600 | Specification Update - Page 40

Instruction if it is Followed by an Instruction That Signals a Floating Point Exception Problem: A MOV SS/POP SS instruction Intel® Architecture Software Developer's Manual, Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 41

to memory early in BIOS code to clear all the global entries from TLB. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 41 Specification Update - Intel E6600 | Specification Update - Page 42

lost or be corrupted in the presence of STPCLK# assertions. Workaround: None Identified. Status: For the steppings affected, see the Summary Tables of Changes. 42 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 43

be generated. However, in the case when the general detect enable flag (GD) bit is set, the observed behavior is that a debug exception (#DB) is generated instead. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 43 Specification Update - Intel E6600 | Specification Update - Page 44

Present to Not Present or from Read/Write to Read Only, etc. • Another processor, without corresponding synchronization and TLB flush, must cause the permission change. 44 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 45

instruction at the lower canonical boundary (0x00007FFFFFFFFFFF) in 64-bit mode, the LBR return registers will save a wrong return address with bits Behavior Problem: Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 45 Specification - Intel E6600 | Specification Update - Page 46

bits become set. Implication: When the temperature reaches an invalid temperature the CPU to Return to a Different Mode Problem: VMLAUNCH/VMRESUME instructions may not fail if the Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification - Intel E6600 | Specification Update - Page 47

: Do not use performance monitoring counters for precise event sampling when the precise event is dependent on the CPL value. Status: For the steppings affected, see the Summary Tables of Changes. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 - Intel E6600 | Specification Update - Page 48

Problem: IA32_PERF_GLOBAL_STATUS MSR (38EH) bit [62] when set, indicates that a PEBS (Precise Event-Based Sampling) overflow has occurred and a PMI (Performance . 48 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 49

Problem: BTM/BTS Branch-From Instruction Address May be Incorrect for Software Interrupts. When BTM (Branch Trace Message) or BTS (Branch Trace Store) is enabled, a software interrupt may result in the overwriting of BTM/BTS branch-from Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo - Intel E6600 | Specification Update - Page 50

AI79. REP Store Instructions in a Specific Situation may cause the Processor to Hang Problem: During a series of REP (repeat) store instructions a store may Changes. 50 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 51

Values Problem: Performance Monitoring counter SIMD_INST_RETIRED (Event: C7H) is used to track retired SSE instructions. Due to this erratum, the processor may Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 51 Specification Update - Intel E6600 | Specification Update - Page 52

Problem: When an unaligned access is performed on paging structure entries, accessing a portion of two different entries simultaneously, the processor may live lock. 52 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 53

Certain Conditions Problem: The INVLPG instruction may not completely bit (A bit) may be set for the subsequent page prior to general protection fault on code segment limit. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 53 Specification - Intel E6600 | Specification Update - Page 54

by NMI#. Implication: A processor that has been taken out of shutdown may have an incorrect EFLAGS, CR0 and CR4. In addition the EXF4 signal may still be asserted. 54 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 55

instruction is affected. Implication: The count value returned by the performance monitoring event SIMD_UOP_TYPE_EXEC.MUL may be lower than expected. The degree of Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 55 Specification Update - Intel E6600 | Specification Update - Page 56

that both o The target linear address corresponds to the modified PDE o The PTE (Page Table Entry) for the target linear address has an A (Accessed) bit that is clear 56 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 57

equal to the address size structure has been processed, external events (such as interrupts) will cause the (E)CX registers to be incremented by a value that Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 57 Specification Update - Intel E6600 | Specification Update - Page 58

subsequent MWAIT instruction. The hardware is triggered on subsequent memory store operations to the monitored address range. Due to this erratum, REP STOS/MOVS fast string operations to the monitored address 58 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 - Intel E6600 | Specification Update - Page 59

with Performance Monitoring Interrupt (PMI) on PEBS buffer overflow enabled and Last Branch Record (LBR) Freeze on PMI enabled by setting FREEZE_LBRS_ON_PMI flag (bit 11) to 1 in IA32_DEBUGCTL (MSR 1D9H), the LBR stack is frozen upon Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo - Intel E6600 | Specification Update - Page 60

old/out-of-date LBR information that Problem: VMCALL failure due to corrupt MSEG location may cause VM Exit to load the machine state incorrectly In systems supporting Intel Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 61

of the erratum condition while the counter is active. Intel has not observed this erratum with any commercially available software. Workaround: None identified. Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 61 Specification Update - Intel E6600 | Specification Update - Page 62

the Summary Tables of Changes. AI114. Problem: A GETSEC[ENTERACCS] Instruction Executed Immediately after GETSEC[WAKEUP] Instruction May Result in a Processor Hang In dual core processor systems supporting Intel® Trusted Execution Technology, a processor hang or unpredictable system behavior may - Intel E6600 | Specification Update - Page 63

FXSAVE May Lead to Memory-Ordering Violations Problem: Under certain conditions, as described in the Software Developers Manual section "Out-of-Order Stores For String Operations in Pentium 4, Intel Xeon, and P6 Family Processors", the processor may perform REP MOVS or REP STOS as write combining - Intel E6600 | Specification Update - Page 64

identified. Intel does not support the use of cacheable and WC memory type aliasing, and WC operations are defined as weakly ordered. Status: For the steppings affected, see the Summary Tables of Changes. 64 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 - Intel E6600 | Specification Update - Page 65

Enabled) is supposed to indicate whether the enable bit in the IA32_MC1_CTL MSR (404H) was set at the time of the last update to the IA32_MC1_STATUS MSR. Due to this Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 65 Specification Update - Intel E6600 | Specification Update - Page 66

Reference", if another exception occurs while attempting to call the double-fault handler, the processor enters shutdown mode. However due to this erratum, only 66 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 67

" VM-entry control in the SMM VMCS to be the value that was in the LMA bit (IA32_EFER.LMA.LMA[bit 10]) in the IA32_EFER MSR (C0000080H) at the time of the last SMM VM Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 67 Specification Update - Intel E6600 | Specification Update - Page 68

. Workaround: It is possible for the BIOS to contain a workaround for this erratum. Status: For the steppings affected, see the Summary Tables of Changes. § 68 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update - Intel E6600 | Specification Update - Page 69

Software Developer's Manual volumes 1,2A, 2B, 3A, and 3B All Specification Changes will be incorporated into a future version of the appropriate Intel® Core™2 Extreme and Intel® Core™2 Duo desktop processor documentation. Δ Intel processor numbers are not a measure of performance. Processor numbers - Intel E6600 | Specification Update - Page 70

to the following documents: • Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Datasheet • Intel® 64 and IA-32 Architectures Software Developer's Manual volumes 1, 2A, 2B, 3A, and 3B All Specification Clarifications will be incorporated into - Intel E6600 | Specification Update - Page 71

Software Developer's manual documentation changes. Follow the link below to become familiar with this file. http://www.intel.com/products/processor/manuals/index.htm § Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence 71 Specification Update

Intel

®

Core

™

2 Extreme Processor

X6800

Δ

and Intel

®

Core

™

2 Duo

Desktop Processor E6000

Δ

and

E4000

Δ

Sequence

Specification Update

—

on 65 nm Process in the 775-land LGA Package supporting

Intel

®

64

Φ

Architecture, Intel

®

Virtualization Technology± and

Intel

®

Trusted Execution Technology

ŧ

December 2010

Notice:

The Intel

®

Core

TM

2 Extreme and Intel

®

Core

TM

2 Duo desktop processor may

contain design defects or errors known as errata which may cause the product to

deviate from published specifications. Current characterized errata are documented in

this Specification Update.

Document Number:

313279-027