Intel E6600 Specification Update - Page 26

A Write to an APIC Register Sometimes May Appear to Have

|

UPC - 735858184625

View all Intel E6600 manuals

Add to My Manuals

Save this manual to your list of manuals |

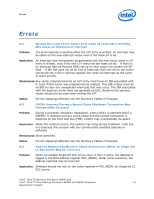

Page 26 highlights

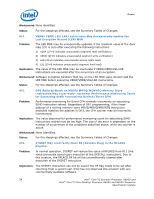

Errata AI10. Single Step Interrupts with Floating Point Exception Pending May Be Mishandled Problem: In certain circumstances, when a floating point exception (#MF) is pending during single-step execution, processing of the single-step debug exception (#DB) may be mishandled. Implication: When this erratum occurs, #DB will be incorrectly handled as follows: • #DB is signaled before the pending higher priority #MF (Interrupt 16) • #DB is generated twice on the same instruction Workaround: None identified. Status: For the steppings affected, see the Summary Tables of Changes. AI11. A Write to an APIC Register Sometimes May Appear to Have Not Occurred Problem: With respect to the retirement of instructions, stores to the uncacheable memory-based APIC register space are handled in a non-synchronized way. For example if an instruction that masks the interrupt flag, e.g. CLI, is executed soon after an uncacheable write to the Task Priority Register (TPR) that lowers the APIC priority, the interrupt masking operation may take effect before the actual priority has been lowered. This may cause interrupts whose priority is lower than the initial TPR, but higher than the final TPR, to not be serviced until the interrupt enabled flag is finally set, i.e. by STI instruction. Interrupts will remain pending and are not lost. Implication: In this example the processor may allow interrupts to be accepted but may delay their service. Workaround: This non-synchronization can be avoided by issuing an APIC register read after the APIC register write. This will force the store to the APIC register before any subsequent instructions are executed. No commercial operating system is known to be impacted by this erratum. Status: For the steppings affected, see the Summary Tables of Changes. AI12. Programming the Digital Thermal Sensor (DTS) Threshold May Cause Unexpected Thermal Interrupts Problem: Software can enable DTS thermal interrupts by programming the thermal threshold and setting the respective thermal interrupt enable bit. When programming DTS value, the previous DTS threshold may be crossed. This will generate an unexpected thermal interrupt. Implication: Software may observe an unexpected thermal interrupt occur after reprogramming the thermal threshold. Workaround: In the ACPI/OS implement a workaround by temporarily disabling the DTS threshold interrupt before updating the DTS threshold value. 26 Intel® Core™2 Extreme Processor X6800 and Intel® Core™2 Duo Desktop Processor E6000 and E4000 Sequence Specification Update