Marantz SR8000 Service Manual - Page 27

Ic Data - reset

|

View all Marantz SR8000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 27 highlights

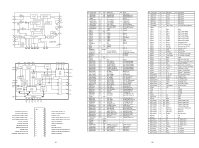

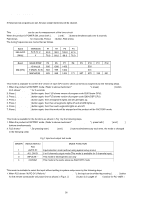

6. IC DATA Q601:YSS912 /CSB SCK SI OPORT0 7 SCK SI SO /CS IPORT0 7 Control signals Microprocessor Interface Control Registers Coefficient / Program RAM /SDBCK0 SDBCK0 SDWCK0 SDIA0 SDIA1 Control signals SDOACKSEL L, R LS, RS C, LFE SDBCK1 SDWCK1 SDIBCKSEL SDOBCKSEL SDOB0 SDOB1 SDOB2 SDOB3 SURENC KARAOKE MUTE CRC AC3DATA DTSDATA NONPCM Data RAM SDOB Interface 24 * 16 Sub DSP SDIB Interface SDIBSEL SDOA Interface 24 * 24 Main DSP AC-3/Pro Logic/DTS Decoder Input Buffer SDIA Interface SDIASEL STREAM 0 7 Operating clock (30MHz) PLL ExternalRAM Interface ERAMUSE OVFB RAMA0 16 RAMOEN RAMWEN RAMCEN RAMD0 7 SDIB3 SDIB2 SDIB1 SDIB0 SDOA2 SDOA1 SDOA0 Delay RAM CRC CPO XO XI No. NAME 1 VDD1 2 RAMCEN 3 RAMA16 4 RAMA15 5 SDIB0 6 SDIB1 7 SDIB2 8 XI 9 XO 10 VSS 11 AVDD 12 SDIB3 13 TEST 14 TEST 15 OVFB 16 DTSDATA 17 AC3DATA 18 SDOB3 19 CPO 20 AVSS 21 VDD2 22 SDOA2 23 SDOA1 24 SDOA0 25 RAMA14 26 RAMA13 27 RAMA12 28 RAMA11 29 RAMA10 30 VSS 31 VDD1 32 OPORT0 33 OPORT1 34 OPORT2 35 OPORT3 36 OPORT4 37 OPORT5 38 OPORT6 39 OPORT7 40 VSS 41 VDD2 42 RAMA9 43 RAMA8 44 RAMA7 45 SDOB2 46 SDOB1 47 SDOB0 48 SDBCK1 49 SDWCK1 50 VSS I/O FUNCTION - +5V power supply (for I/Os) O External SRAM Interface /CE O External SRAM Interface address 16 O External SRAM Interface address 15 I+ PCM input 0 to Sub DSP I+ PCM input 1 to Sub DSP I+ PCM input 2 to Sub DSP I Crystal oscillator connection or input external clock (12.288 MHz) o Crystal oscillator connection - Ground - +3.3V power supply (for PLL circuit) I+ PCM input 3 to Sub DSP Test terminal (to be open in normal use) Test terminal (to be open in normal use) O Detection of overflow at Sub DSP O DTS data detection (Refer to "Status Register".) O AC-3 data detection (Refer to "Status Register" .) O PCM output from Sub DSP A Output terminal for PLL, to be connected to ground through the external analog filter circuit. (Refer to "External Circuit for PLL" .) - Ground (for PLL circuit) - +3.3V power supply (for core logic) o PCM output from Main DSP (C, LFE) O PCM output from Main DSP (LS, RS) O PCM output from Main DSP (L, R) O External SRAM Interface address 14 O External SRAM Interface address 13 O External SRAM Interface address 12 O External SRAM Interface address 11 O External SRAM Interface address 10 - Ground - +5V power supply (for I/Os) O Output port for general purpose. (Refer to " OPORT Register") O Output port for general purpose. (Refer to " OPORT Register") O Output port for general purpose. (Refer to " OPORT Register") O Output port for general purpose. (Refer to " OPORT Register") O Output port for general purpose. (Refer to " OPORT Register") O Output port for general purpose. (Refer to " OPORT Register") O Output port for general purpose. (Refer to " OPORT Register") O Output port for general purpose. (Refer to " OPORT Register") - Ground - +3.3V power supply (for core logic) O External SRAM interface address 9 O External SRAM interface address 8 O External SRAM interface address 7 O PCM output from Sub DSP O PCM output from Sub DSP O PCM output from Sub DSP I+ Bit clock input for SDOA, SDIB, SDOB. (Refer to " SDOA, SDIB, SDOB Register") I+ Word clock input for SDOA, SDIB, SDOB. (Refer to " SDOA, SDIB, SDOB Register") - Ground No. NAME I/O FUNCTION 51 VDD2 - +3.3V power supply (for core logic) 52 NONPCM O Detection of non PCM data. (Refer to " Status Register") 53 CRC O Detection of AC-3 CRC error. (Refer to " Status Register") 54 MUTE O Detection of auto-mute. (Refer to " Status Register") 55 KARAOKE O Detection of AC-3 karaoke data. (Refer to " Status Register") 56 SURENC O Detection of AC-3 2/0 mode Dolby surround encoded input (Refer to " Status Register") 57 /SDBCK0 O Inverted SDBCKO clock output (refer to " Block diagram") 58 RAMA6 O External SRAM Interface address 6 59 RAMA5 O External SRAM Interface address 5 60 VSS - Ground 61 RAMA4 O External SRAM Interface address 4 62 /lC Is Initial clear 63 TEST Test terminal (to be open in normal use) 64 RAMA3 O External SRAM Interface address 3 65 /CSB Is+ Sub DSP Chip select 66 /CS Is Microprocessor interface Chip select 67 SO Ot Microprocessor interface Serial data output 68 SI Is Microprocessor interface/Sub DSP Serial data input 69 SCK Is Microprocessor interface/Sub DSP clock input 70 RAMA2 O External SRAM Interface address 2 71 VDD1 - +5V power supply (for I/Os) 72 RAMD0 I+/O External SRAM Interface data (STREAM 0 output when External SRAM is not in use) 73 RAMD1 I+/O External SRAM Interface data (STREAM 1 output when External SRAM is not in use) 74 RAMD2 I+/O External SRAM Interface data (STREAM 2 output when External SRAM is not in use) 75 RAMD3 I+/O External SRAM Interface data (STREAM 3 output when External SRAM is not in use) 76 RAMD4 I+/O External SRAM Interface data (STREAM 4 output when External SRAM is not in use) 77 RAMD5 I+/O External SRAM Interface data (STREAM 5 output when External SRAM is not in use) 78 RAMD6 I+/O External SRAM Interface data (STREAM 6 output when External SRAM is not in use) 79 RAMD7 I+/O External SRAM Interface data (STREAM 7 output when External SRAM is not in use) 80 VSS - Ground 81 VDD2 - +3.3V power supply (for core logic) 82 SDWCK0 I Word clock input for SDIA, SDOA, SDIB, SDOB (Refer to " SDIA, SDOA, SDIB, SDOB Register") 83 SDBCK0 I Bit clock input for SDIA SDOA SDIB SDOB (Refer to " SDIA, SDOA, SDIB, SDOB Register") 84 SDIA0 I AC-3/DTS bitstream (or PCM) data input for Main DSP (Refer to " SDIA Register") 85 SDIA1 I AC-3/DTS bitstream (or PCM) data input for Main DSP (Refer to " SDIA Register") 86 RAMA1 O External SRAM Interface address 1 87 RAMA0 O External SRAM Interface address 0 88 RAMWEN O External SRAM Interface /WE 89 RAMOEN O External SRAM Interface /OE 90 VSS - Ground 91 VDD2 - +3.3V power supply (for core logic) 92 IPORT7 I+ Input port for general purpose (Refer to " IPORT Register") 93 IPORT6 I+ Input port for general purpose (Refer to " IPORT Register") 94 IPORT5 I+ Input port for general purpose (Refer to " IPORT Register") 95 IPORT4 I+ Input port for general purpose (Refer to " IPORT Register") 96 IPORT3 I+ Input port for general purpose (Refer to " IPORT Register") 97 IPORT2 I+ Input port for general purpose (Refer to " IPORT Register") 98 IPORT1 I+ Input port for general purpose (Refer to " IPORT Register") 99 IPORT0 I+ Input port for general purpose (Refer to " IPORT Register") 100 VSS Ground Note ) Is : Schmidt trigger input terminal I+ : Input terminal with a pull-up resistor O : Digital output terminal Ot : Tri-state digital output terminal A : Analog terminal QD01:AD1855 CONTROL DATA VOLUME INPUT MUTE 3 DIGITAL SUPPLY CLOCK IN 96/48FS CLOCK 2 AD1855 SERIAL CONTROL INTERFACE VOLTAGE REFERENCE 16-/18-/20-/24-BIT 3 DIGITAL DATA INPUT SERIAL 2 MODE SERIAL DATA INTERFACE ATTEN/ MUTE ATTEN/ MUTE 83 INTERPOLATOR 83 INTERPOLATOR PD /RST MUTE MULTIBIT SIGMADELTA MODULATOR MULTIBIT SIGMADELTA MODULATOR DAC DAC DE-EMPHASIS 2 ANALOG SUPPLY CLOCK CIRCUIT OUTPUT BUFFER OUTPUT BUFFER 2 ZERO FLAG Pin 1 2 384/ 256 3 4 X2MCLK 5 ANALOG 6 OUTPUTS 7 8 9 Input/Output I I I I I I I O I DGND 1 28 DVDD MCLK 2 27 SDATA CLATCH 3 26 BCLK CCLK 4 25 L/RCLK CDATA 5 24 PD/RST 384/256 X2MCLK ZEROR 6 AD1855 23 MUTE 7 TOP VIEW 22 ZEROL 8 (Not to Scale) 21 IDPM0 DEEMP 9 20 IDPM1 96/48 10 19 FILTB AGND 11 18 AVDD OUTR+ 12 17 OUTL+ OUTRÐ 13 16 OUTLÐ FILTR 14 15 AGND 47 10 I 11, 15 I 12 O 13 O 14 O 16 O 17 O 18 I 19 O 20 I 21 I 22 O 23 I 24 I 25 I 26 I 27 I 28 I Pin Name DGND MCLK CLATCH CCLK CDATA 384/256 X2MCLK ZEROR DEEMP 96/ 48 AGND OUTR+ OUTRÐ FILTR OUTLÐ OUTL+ AVDD FILTB I DPM1 I DPM0 ZEROL MUTE PD/RST L /RCLK BCLK SDATA DVDD Description Digital Ground. Master Clock Input. Connect to an external clock source at either 256, 384 or 512 FS . Latch input for control data. This input is rising-edge sensitive. Control clock input for control data. Control input data must be valid on the rising edge of CCLK. CCLK may be continuous or gated. Serial control input, MSB first, containing 16 bits of unsigned data per channel. Used for specifying channel specific attenuation and mute. Selects the master clock mode as either 384 times the intended sample frequency (HI) or 256 times the intended sample frequency (LO). The state of this input should be hardwired to logic HI or logic LO, or may be changed while the AD1855 is in power-down/reset. It must not be changed while the AD1855 is operational. Selects internal clock doubler (LO) or internal clock = MCLK (HI). Right Channel Zero Flag Output. This pin goes HI when Right Channel has no signal input for more than 1024 LR Clock Cycles. De-Emphasis. Digital de-emphasis is enabled when this input signal is HI. This is used to impose a 50ms/15 ms response characteristic on the output audio spectrum at an assumed 44.1 kHz sample rate. Selects 48 kHz (LO) or 96 kHz Sample Frequency Control. Analog Ground. Right Channel Positive line level analog output. Right Channel Negative line level analog output. Voltage Reference Filter Capacitor Connection. Bypass and decouple the voltage reference with parallel 10 m F and 0.1 m F capacitors to the AGND. Left Channel Negative line level analog output. Left Channel Positive line level analog output. Analog Power Supply. Connect to analog +5 V supply. Filter Capacitor connection, connect 10 m F capacitor to AGND. Input serial data port mode control one. With IDPM0, defines one of four serial modes. Input serial data port mode control zero. With IDPM1, defines one of four serial modes. Left Channel Zero Flag output. This pin goes HI when Left Channel has no signal input for more than 1024 LR Clock Cycles. Mute. Assert HI to mute both stereo analog outputs. Deassert LO for normal operation. Power-Down/Reset. The AD1855 is placed in a low power consumption mode when this pin is held LO. The AD1855 is reset on the rising edge of this signal. The serial control port registers are reset to the default values. Connect HI for normal operation. Left/ Right clock input for input data. Must run continuously. Bit clock input for input data. Need not run continuously; may be gated or used in a burst fashion. Serial input, MSB first, containing two channels of 16, 18, 20, and 24 bits of twos complement data per channel. Digital Power Supply Connect to digital +5 V supply. Q351:LC72722 48