Asus P I-P55T2P4 User Manual - Page 18

System Memory DRAM & SRAM

|

View all Asus P I-P55T2P4 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 18 highlights

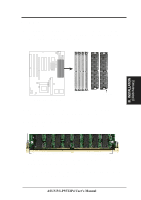

III. INSTALLATION 2. System Memory (DRAM & SRAM) This motherboard supports four 72-pin SIMMs of 4MB, 8MB, 16MB, 32MB, or 64MB to form a memory size between 8MB to 256MB. The DRAM can be either 60ns or 70ns Fast Page Mode (Asymmetric or Symmetric) or EDO. To support ECC, you must use true (opposed to phantom parity generated by logic chips) 36-bit parity-type DRAM (e.g. 8 chips + 4 parity chips) in pairs for all modules. Mixing 32-bit non-parity DRAM (e.g. 8 chips) and 36-bit DRAM (e.g. 12 chips) will work minus the ECC feature. Install memory in any or all of the banks in any combination as follows: Bank Bank 0 SIMM Sockets 1&2 Memory Module 4MB, 8MB, 16MB, 32MB, 64MB 72-pin FPM or EDO SIMM Total Memory x2 Bank 1 4MB, 8MB, 16MB, 32MB, 64MB x2 SIMM Sockets 3&4 72-pin FPM or EDO SIMM Total System Memory = III. INSTALLATION (Memory) IMPORTANT: Memory setup is required in BIOS Chipset Setup "Auto Configuration" on page 34. IMPORTANT: Each bank must have the same size memory installed in pairs. Do not use memory modules with more than 24 chips per module. Modules with more than 24 chips exceed the design specifications of the memory subsystem and will be unstable. TAG SRAM Upgrade: The purpose of this SRAM is described by "Memory Cacheable Size" jumper. You must use a standard 5Volt SRAM chip that is 15ns or faster. Notch Indention Insert one 16K8 or 32K8 SRAM chip as shown by the Top view with the semicircle "Indention" on the same side as the "Notch." Top Side TAG SRAM Upgrade WARNING: If the cache module that you install already have an extended tag, do not install another TAG SRAM into the TAG SRAM Upgrade Socket. 12 ASUS P/I-P55T2P4 User's Manual