Compaq ProLiant 8000 Compaq ProLiant 8000 Server Technology - Page 10

Pentium III Xeon Processor Technology, Level 2 Cache, Katmai Core Logic

|

View all Compaq ProLiant 8000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 10 highlights

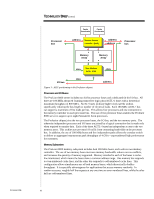

TC000603TB TECHNOLOGY BRIEF (cont.) ... Pentium III Xeon Processor Technology The Pentium III Xeon processor is based on the Pentium II Xeon processor cartridge form factor. The Pentium III Xeon processor provides a higher internal core frequency than the Pentium II Xeon processor and includes 70 new streaming instructions that permit more efficient use of memory above 4 GB. The Pentium III Xeon processor includes the following features: • Minimum 550-MHz core frequency • 330-contact slot connector form factor (formerly called Slot 2) • Full-speed cache on module • 512-KB (550-MHz only), 1-MB, or 2-MB Level 2 (L2) cache • Katmai core logic Level 2 Cache Each Pentium III Xeon processor includes an L2 cache sized at 512 KB, 1 MB, or 2 MB that operates on a full-speed backside bus. The large cache size and full-speed backside bus enable very efficient access to the most frequently used data. This reduces traffic on the host bus and notably enhances performance. Katmai Core Logic Aside from speed and cache size increases, the main difference between the Pentium II Xeon and Pentium III Xeon processors is the migration to the Katmai core logic. The Katmai core logic adds the following enhancements to the existing Intel core: • Memory streaming • Concurrent Single Instruction Multiple Data - Floating Point (SIMD-FP) • Katmai New Instructions (KNI) Memory Streaming Memory streaming is a set of techniques that increase the utilization of the memory bus during memory reads and writes. Processors must frequently wait for data not stored in cache memory to be retrieved from system memory. Because the system bus connecting the memory to the processor is slower than the processor core speed, this results in a performance bottleneck. Katmai's memory streaming enables the processor to prefetch data from system memory to cache memory. During writes to memory, other new instructions can tell the processor to bypass the L2 cache and write data directly back to memory. Bypassing the L2 cache frees room in the cache for more data. This technique is useful when the software programmer knows in advance that the data will not be requested again in the near future. Concurrent SIMD-FP Concurrent SIMD-FP applies the same architecture used by MMX for integer operations to floating-point numbers. Floating-point numbers are used extensively in 3D graphics and scientific computations. Katmai processors have eight new registers that can each hold four single-precision floating-point numbers. Once the registers are filled, a single instruction can be used to add, subtract, or do other operations between the registers. For example, eight floating-point numbers could be added together using one instruction call. 10