Compaq ProLiant 8000 Compaq ProLiant 8000 Server Technology - Page 8

Compaq Host-to-PCI Bridges, cont., ProLiant, PCI Local Bus Specification

|

View all Compaq ProLiant 8000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 8 highlights

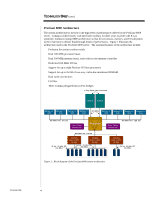

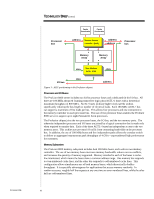

TC000603TB TECHNOLOGY BRIEF (cont.) ... Compaq Host-to-PCI Bridges The Compaq host-to-PCI bridges included in the ProLiant 8000 server were engineered to enhance performance of the Profusion chipset. They include the following features: • 64-bit, 66-MHz PCI support with a theoretical peak throughput of 533 MB/s • Delayed transaction support • Asynchronous design to accommodate multiple bus frequencies • Multiple prefetch buffers • PCI Hot Plug technology • Peer-to-peer transaction support 64-Bit, 66-MHz PCI Support Compaq licensed the host-to-PCI bridges to Intel, and they will ship with a Compaq logo on top in servers produced by other original equipment manufacturers. The bridges are compliant with the PCI 2.2 Specification1 and support 64-bit, 66-MHz PCI transactions. The ProLiant 8000 server supports three bridges with up to eleven I/O expansion slots. PCI Bus 1 operates at 33 MHz and includes one 32-bit PCI Hot Plug slot and three 64-bit PCI Hot Plug slots. PCI Bus 2 is also a 33-MHz bus and includes five 64-bit PCI Hot Plug slots. PCI Bus 3 operates at 66 MHz with two 64-bit PCI Hot Plug slots. The Compaq 8-way architecture will support up to four Compaq host-to-PCI bridges. However, by incorporating only three host-to-PCI bridges, the ProLiant 8000 server has room on the I/O board to deliver an additional PCI slot, a meaningful advantage for enterprise customers who consistently request additional capacity. Delayed Transactions One of the most important features of Compaq's host-to-PCI bridge is that it supports delayed PCI transactions, which improve bus performance. In a delayed PCI transaction, the device that initiates the transaction polls the host-to-PCI bridge to determine if the requested data is there, rather than holding the bus while waiting for the data. This allows other devices to use the bus while the transaction is completed. To further improve bus efficiency, Compaq built in additional features to reduce the amount of polling. Asynchronous Design The bridge is split into two sections: upstream (host I/O side) and downstream (PCI side). All the functions on the upstream side are in the host processor clock domain at 100 MHz. All functions on the downstream side are in the PCI clock domain at up to 66 MHz. This asynchronous design is a flexible solution for supporting multiple clock speeds. Multiple Prefetch Buffers The Compaq host-to-PCI bridge is designed with multiple prefetch buffers to ensure optimum I/Oto-processor performance. Each buffer can hold multiple cache lines. These buffers are sized to provide optimal performance at a reasonable and cost-effective die size. Because of the delayed transaction support, the bridge can get data for multiple PCI devices concurrently. Other controllers can hold only a single cache line and a single request at a time. 1PCI Local Bus Specification, Revision 2.2, announced January 25, 1999, PCI Special Interest Group. 8