HP X Class 500/550MHz hp visualize workstation - SDRAM Advantages with the HP - Page 8

cache lines. This means that, on the average, the CPU executes out of cache for 260

|

View all HP X Class 500/550MHz manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 8 highlights

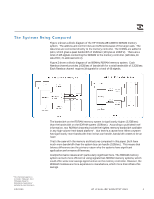

1/5/2000 Figure 4 shows a timing diagram of the address and data signals on the system bus. Key points here include: • Three addresses are sent to the memory controller before the first data is returned. • The first data for the RDRAM memory system is returned 140 ns after the first address. (This includes four states of overhead for the CPU.) • The first data for the SDRAM memory system is returned 97.5 ns after the first address. (This includes four states of overhead for the CPU.) • Four system bus clocks (30ns) are needed to return the 32 byte cache line. (The data bus is 8 bytes wide.) • The CPU spends an average of 222.5 ns filling the three cache lines on the RDRAM memory system. • For the SDRAM system, the CPU spends an average of 180 ns filling the cache. For this example, there were 15 misses or cache line fills for each 1,300 CPU clocks spent executing out of cache. These 15 misses, on the average, were a burst of three cache lines. This means that, on the average, the CPU executes out of cache for 260 clocks between each burst of three misses. Figure 5 shows the difference in application performance for RDRAM vs. 133MHz SDRAM. Key points here include: • Both systems spend the same amount of time in cache (350 ns). • The RDRAM system spends 222.5 ns filling the cache vs. 180 ns for the SDRAM system. • The total time is 572.5 ns for RDRAM and 530 ns for SRDRAM. • The performance difference is (572.5-530)/530*100% = 8%. HP VISUALIZE WORKSTATIONS 7