Nintendo 1504166 Programming Manual - Page 142

UART Communication Functions, a fixed 1 bit.

|

View all Nintendo 1504166 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 142 highlights

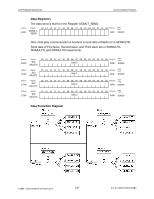

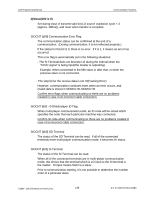

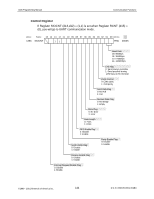

AGB Programming Manual Communication Functions 13.3 UART Communication Functions UART communications can be illustrated using the following drawing. SI SI SO SO SD SD SC SC In UART communication mode, a HI level is output from the SD terminal. When the receive data register (or the receive FIFO) is full, a HI is output from the SD terminal. When it is not full, a LO is output from the SD terminal if the receive enable flag is set. A HI is output if it is reset. The output of the SD terminal of the other machine is input to the SC terminal. Once data is written to the send data register, data is sent after a "Start bit" (1 bit) is sent from the SO terminal. However, when the CTS flag for the Control Register is set, data can be sent only when there is a LO input to the SC terminal. The Stop bit is a fixed 1 bit. Data Register Address 12Ah Register SIO DATA8 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes R/W Initial Value 0000h Relations Between Data Register, FIFO, and Shift Register When sending or receiving, there are 4 bytes of FIFO. By using the FIFO enable flag for the control register SIOCNT, you can select whether to use or not use FIFO. When FIFO is not Used If written to a data register SIODATA8, data is written to a send shift register, and if read, data is read from a receive shift register. (Only the lower 8 bits are valid.) ©1999 - 2001 Nintendo of America Inc. 142 D.C.N. AGB-06-0001-002B4