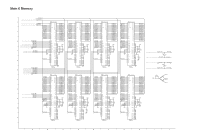

Panasonic CF-73SCUTSBM Service Manual - Page 61

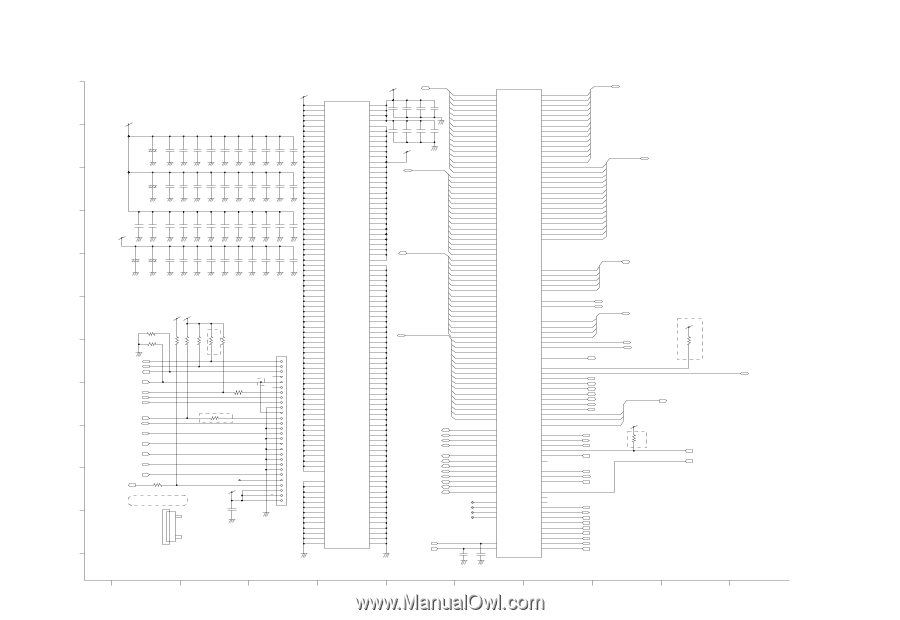

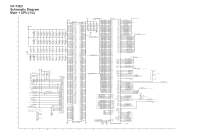

CF-73, Schematic Diagram, Main 1 CPU 1/2, E3

|

UPC - 092281843346

View all Panasonic CF-73SCUTSBM manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 61 highlights

CF-73E3 Schematic Diagram Main 1 CPU (1/2) VC18 003:F6 GTLD3_HD#[48-63] Banias 1.4G IC1 003:I1 VCPUCORE GTLD3_HD#[63] AF26 D#[63] A#[3] P4 GTLA0_HA#[3] Banias 1.4G IC1 GTLD3_HD#[62] AF22 D#[62] A#[4] U4 GTLA0_HA#[4] 1 D6 VCC_CORE VCCA[0] F26 GTLD3_HD#[61] AF25 D#[61] A#[5] V3 GTLA0_HA#[5G] TLA0_HA#[3-16] D8 VCC_CORE D18 VCC_CORE VCCA[1] B1 VCCA[2] N1 C49 C51 C53 C55 0.01u 0.01u 0.01u 0.01u GTLD3_HD#[60] GTLD3_HD#[59] AD21 D#[60] AE21 D#[59] A#[6] R3 A#[7] V2 GTLA0_HA#[6] GTLA0_HA#[7] VCPUCORE D20 VCC_CORE D22 VCC_CORE E5 VCC_CORE VCCA[3] VCCP VCCP AC26 D10 D12 6.3V 6.3V 6.3V 6.3V GTLD3_HD#[58] GTLD3_HD#[57] GTLD3_HD#[56] AF20 D#[58] AD24 D#[57] AF23 D#[56] A#[8] W1 A#[9] T4 A#[10] W2 GTLA0_HA#[8] GTLA0_HA#[9] GTLA0_HA#[10] E7 VCC_CORE E9 VCC_CORE VCCP D14 VCCP D16 B C50 B C52 B C54 B C56 10u 10u 10u 10u 2125 2125 2125 2125 GTLD3_HD#[55] GTLD3_HD#[54] AE22 D#[55] AD23 D#[54] A#[11] Y4 A#[12] Y1 GTLA0_HA#[11] GTLA0_HA#[12] 2 SP-CAP + 2V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V E17 VCC_CORE E19 VCC_CORE VCCP E11 VCCP E13 VCCP GTLD3_HD#[53] GTLD3_HD#[52] AC25 D#[53] AC22 D#[52] A#[13] U1 A#[14] AA3 GTLA0_HA#[13] GTLA0_HA#[14] C1 100u D B C7 B C11 B C15 B C19 B C24 B C29 B C33 B C37 B C41 B C45 10u 10u 10u 10u 10u 10u 10u 10u 10u 10u 2125 2125 2125 2125 2125 2125 2125 2125 2125 2125 E21 VCC_CORE F6 VCC_CORE VCCP E15 VCCP F10 GTLD3_HD#[51] GTLD3_HD#[50] AC20 D#[51] AB24 D#[50] A#[15] Y3 A#[16] AA2 GTLA0_HA#[15] GTLA0_HA#[16] GTLA1_HA#[17-31] 003:I2 F8 VCC_CORE F18 VCC_CORE VCCP F12 VCCP F14 003:F5 GTLD2_HD#[32-47] GTLD3_HD#[49] GTLD3_HD#[48] AC23 D#[49] AB25 D#[48] A#[17] AF4 A#[18] AC4 GTLA1_HA#[17] GTLA1_HA#[18] F20 VCC_CORE VCCP F16 GTLD2_HD#[47] Y25 D#[47] A#[19] AC7 GTLA1_HA#[19] 3 SP-CAP + 2V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V C2 B C8 B C12 B C16 B C20 B C25 B C30 B C34 B C38 B C42 B C46 NU 10u 10u 10u 10u 10u 10u 10u 10u 10u 10u F22 VCC_CORE G5 VCC_CORE G21 VCC_CORE VCCP K6 VCCP L5 VCCP L21 D 2125 2125 2125 2125 2125 2125 2125 2125 2125 2125 H6 VCC_CORE VCCP M6 GTLD2_HD#[46] GTLD2_HD#[45] GTLD2_HD#[44] GTLD2_HD#[43] AA26 D#[46] Y23 D#[45] V26 D#[44] U25 D#[43] A#[20] AC3 A#[21] AD3 A#[22] AE4 A#[23] AD2 GTLA1_HA#[20] GTLA1_HA#[21] GTLA1_HA#[22] GTLA1_HA#[23] H22 VCC_CORE VCCP M22 GTLD2_HD#[42] V24 D#[42] A#[24] AB4 GTLA1_HA#[24] J5 VCC_CORE VCCP N5 GTLD2_HD#[41] U26 D#[41] A#[25] AC6 GTLA1_HA#[25] J21 VCC_CORE VCCP N21 GTLD2_HD#[40] AA23 D#[40] A#[26] AD5 GTLA1_HA#[26] K22 VCC_CORE VCCP P6 GTLD2_HD#[39] R23 D#[39] A#[27] AE2 GTLA1_HA#[27] 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V U5 VCC_CORE VCCP P22 GTLD2_HD#[38] R26 D#[38] A#[28] AD6 GTLA1_HA#[28] 4 VCCP B C4 B C5 10u 10u B C9 B C13 B C17 B C21 B C26 B C31 B C35 B C39 B C43 B C47 10u 10u 10u 10u 10u 10u 10u 10u 10u 10u 2125 2125 2125 2125 2125 2125 2125 2125 2125 2125 2125 2125 V6 VCC_CORE V22 VCC_CORE W5 VCC_CORE VCCP R5 VCCP R21 VCCP T6 GTLD2_HD#[37] GTLD2_HD#[36] GTLD2_HD#[35] R24 D#[37] V23 D#[36] U23 D#[35] A#[29] AF3 A#[30] AE1 A#[31] AF1 GTLA1_HA#[29] GTLA1_HA#[30] GTLA1_HA#[31] W21 VCC_CORE VCCP T22 GTLD2_HD#[34] T25 D#[34] SP-CAP SP-CAP + 2V + 2V C3 C6 100u NU D D C10 C14 C18 C22 C27 C32 C36 C40 C44 C48 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u 0.1u Y6 VCC_CORE Y22 VCC_CORE AA5 VCC_CORE AA7 VCC_CORE AA9 VCC_CORE VCCP U21 VCCQ[0] P23 VCCQ[1] W4 GND F1 GND E25 003:F3 GTLD1_HD#[16-31] GTLD2_HD#[33] GTLD2_HD#[32] GTLD1_HD#[31] GTLD1_HD#[30] GTLD1_HD#[29] AA24 D#[33] Y26 D#[32] K25 D#[31] N25 D#[30] H26 D#[29] REQ#[0] R2 GTLA0_HREQ#[0-4] GTLA0_HREQ#[0] 003:I5 5 AA11 VCC_CORE GND E22 GTLD1_HD#[28] M25 D#[28] REQ#[1] P3 GTLA0_HREQ#[1] AA13 VCC_CORE GND E20 GTLD1_HD#[27] N24 D#[27] REQ#[2] T2 GTLA0_HREQ#[2] AA15 VCC_CORE GND E18 GTLD1_HD#[26] L26 D#[26] REQ#[3] P1 GTLA0_HREQ#[3] AA17 VCC_CORE GND E16 GTLD1_HD#[25] J25 D#[25] REQ#[4] T1 GTLA0_HREQ#[4] AA19 VCC_CORE GND E14 GTLD1_HD#[24] M23 D#[24] AA21 VCC_CORE AB6 VCC_CORE GND E12 GND E10 GTLD1_HD#[23] GTLD1_HD#[22] J23 D#[23] G24 D#[22] ADSTB#[0] U3 ADSTB#[1] AE5 GTLA0_ADSTB#[0] GTLA1_ADSTB#[1] 003:I5 003:I5 AB8 VCC_CORE GND E8 GTLD1_HD#[21] F25 D#[21] BPM#[0-3] 6 VC3 VCCP CPU 0.5" AB10 VCC_CORE AB12 VCC_CORE GND E3 GND D26 GTLD1_HD#[20] GTLD1_HD#[19] H24 D#[20] M26 D#[19] BPM#[0] C8 BPM#[0] 001:A10,001:A9,001:A9,001:A9 AB14 VCC_CORE GND D23 GTLD1_HD#[18] L23 D#[18] BPM#[1] B8 BPM#[1] VCCP R1 680 * R4 R5 R6 R7 R9* AB16 VCC_CORE AB18 VCC_CORE GND D21 GND D19 003:F1 GTLD0_HD#[0-15] GTLD1_HD#[17] GTLD1_HD#[16] G25 D#[17] H23 D#[16] BPM#[2] A9 BPM#[3] C9 BPM#[2] BPM#[3] R3 27.4 NU 54.9 39.2 150 NU AB20 VCC_CORE GND D17 1% 1% ITP700FLEX CN1* NU AB22 VCC_CORE AC9 VCC_CORE GND D15 GND D13 AC11 VCC_CORE GND D11 7 001:G11 TDI# 1 AC13 VCC_CORE GND D9 GTLD0_HD#[15] GTLD0_HD#[14] GTLD0_HD#[13] GTLD0_HD#[12] GTLD0_HD#[11] C25 D#[15] E23 D#[14] B23 D#[13] C26 D#[12] E24 D#[11] PRDY# A10 PREQ# B10 ADS# N2 GTL_ADS# GTL_PRDY# PREQ# 003:I4 001:A9 001:A8 R12 CPU 0.5" 56 001:G11 TMS# 2 AC15 VCC_CORE GND D7 GTLD0_HD#[10] D24 D#[10] IERR# A4 001:G11 TRST# 3 AC17 VCC_CORE GND D5 CPU 4 AC19 VCC_CORE GND D2 001:G10 TCK# 5 AD8 VCC_CORE GND C24 001:G11 TDO# R10 * NU 6 7 AD10 VCC_CORE AD12 VCC_CORE GND C21 GND C18 009:G4 ITP_BCLK1 8 AD14 VCC_CORE GND C15 ITP_BCLK0 8 009:G4 9 AD16 VCC_CORE GND C13 10 AD18 VCC_CORE GND C10 001:I9;003:J8 GTL_CPURST# R8 * NU 11 AE9 VCC_CORE GND C7 12 AE11 VCC_CORE GND C4 001:H7 PREQ# 13 AE13 VCC_CORE GND C1 GTLD0_HD#[9] GTLD0_HD#[8] GTLD0_HD#[7] GTLD0_HD#[6] GTLD0_HD#[5] GTLD0_HD#[4] GTLD0_HD#[3] GTLD0_HD#[2] GTLD0_HD#[1] GTLD0_HD#[0] B24 D#[9] C20 D#[8] B20 D#[7] A21 D#[6] B26 D#[5] A24 D#[4] B21 D#[3] A22 D#[2] A25 D#[1] A19 D#[0] BR0# N4 BPRI# J3 BNR# L1 LOCK# J2 HIT# K3 HITM# K4 DEFER# L4 TRDY# M3 RS#[0] H1 RS#[1] K1 RS#[2] L2 GTL_BPRI# GTL_BNR# GTL_HLOCK# GTL_HIT# GTL_HITM# GTL_DEFER# GTL_HTRDY# 003:I6 003:I6 003:I6 003:I6 003:I6 003:I6 003:I7 GTL_RS#[0] GTL_RS#[1] GTL_RS#[2] GTL_RS#[0-2] VCCP 003:I7,003:I7,003:I7 CPU_BR0# 003:I8 CPU 0.5" 14 GTL_PRDY# 15 001:H7 16 BPM#[3] 17 9 001:H6 18 BPM#[2] 19 001:H6 20 BPM#[1] 21 001:H6 22 001:H6 BPM#[0] 028:C4 R2 * DBRESET# 10 NU 23 TP1 24 25 VCCP 26 27 AE15 AE17 AE19 AF8 AF10 AF12 AF14 AF16 AF18 VCC_CORE VCC_CORE VCC_CORE VCC_CORE VCC_CORE VCC_CORE VCC_CORE VCC_CORE VCC_CORE A2 GND A5 GND A8 GND F19 GND GND B25 GND B22 GND B19 GND B16 GND B12 GND B9 GND B6 GND B3 GND A26 GND A23 GND A20 GND A17 GND A14 GND A11 003:I9 003:I9 003:I9 003:I9 003:G9 003:G9 003:G9 003:G9 003:G9 003:G9 003:G9 003:G10 GTLD0_DBI#[0] GTLD1_DBI#[1] GTLD2_DBI#[2] GTLD3_DBI#[3] GTLD0_DSTBN#[0] GTLD0_DSTBP#[0] GTLD1_DSTBN#[1] GTLD1_DSTBP#[1] GTLD2_DSTBN#[2] GTLD2_DSTBP#[2] GTLD3_DSTBN#[3] GTLD3_DSTBP#[3] D25 DINV#[0] J26 DINV#[1] T24 DINV#[2] AD20 DINV#[3] C23 DSTBN#[0] C22 DSTBP#[0] K24 DSTBN#[1] L24 DSTBP#[1] W25 DSTBN#[2] W24 DSTBP#[2] AE24 DSTBN#[3] AE25 DSTBP#[3] A20M# C2 FERR# D3 IGNNE# A3 PWRGOOD E4 SMI# B4 DBR# A7 DBSY# M2 DRDY# H2 INIT# B5 RESET# B11 ITP_CLK0 A16 CPU_A20M# CPU_FERR# CPU_IGNNE# CPU_SMI# 010:D4 010:E4 010:D4 010:D5 GTL_DBSY# GTL_DRDY# CPU_INIT# 003:I7 003:I7 002:G5;010:D4 R11 330 CPU 0.5" CPU_PWRGD GTL_CPURST# 010:D4 001:A8;003:J8 Note:* ITP NU 28 F21 GND GND F17 TP2 B2 RSVD4(Key) ITP_CLK1 A15 52435-2891 F24 GND GND F15 C28 * Molex G2 GND GND F13 1pin NU G6 GND GND F11 TP3 AF7 RSVD3 TP4 C3 RSVD2 TP5 C14 RSVD1 TCK A13 TDO A12 TDI C12 TCK# TDO# TDI# 001:A8 001:A8 001:A7 G22 GND GND F9 TMS C11 TMS# 001:A7 G23 GND GND F7 TRST# B13 TRST# 001:A7 11 G26 GND GND F5 LINT[0]/INTR D1 CPU_INTR 010:D4 28pin H3 GND GND F4 LINT[1]/NMI D4 CPU_NMI 010:D4 H5 GND GND E6 009:G3 CPU_BCLK0 B15 BCLK[0] STPCLK# C6 CPU_STPCLK# 010:D5 INTEL uFC-BGA479 RJ80535GC0171MSL6F5 009:G3 CPU_BCLK1 C57 C58 NU NU B14 BCLK[1] SLP# A6 CPU_SLP# 010:D5 INTEL RJ80535GC0171MSL6F5 uFC-BGA479 A B C D E F G H I J