Biostar TA780G M2 Bios Setup - Page 26

GPP Slots Power Limit, W, Port #04/07 Features, Gen2 High Speed Mode, Link ASPM - + bios update

|

View all Biostar TA780G M2 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 26 highlights

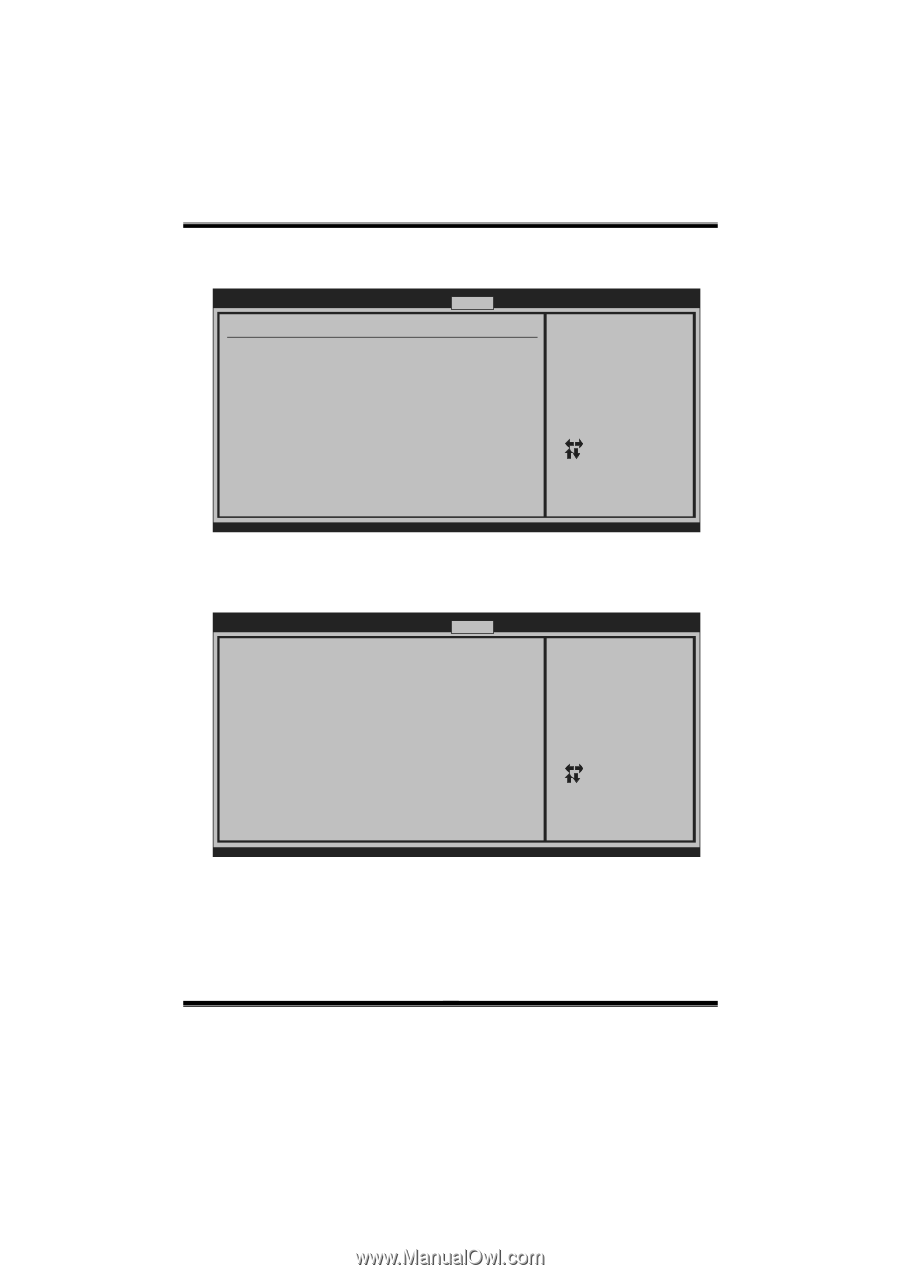

TA780G M2+ BIOS Manual PCI Express Configuration PCI Express Configuration GPP Slots Power Limit, W > Port #04 Features > Port #07 Features > NB-SB Port Features BIOS SETUP UTILITY Chipset [25 ] Select Screen Select Item EnterUpdate F1 General Help F10 Save and Exit ESC Exit vxx.xx (C)Copyright 1985-200x, American Megatrends, Inc. GPP Slots Power Limit, W Options: 25 (Default) / 0-255 Port #04/07 Features Gen2 High Speed Mode Link ASPM BIOS SETUP UTILITY Chipset [Disabled] [Disabled] Auto - RC only advertize Gen2 capability. Select Screen Select Item +- Change Option F1 General Help F10 Save and Exit ESC Exit vxx.xx (C)Copyright 1985-200x, American Megatrends, Inc. Gen2 High Speed Mode Options: Disabled (Default) / Software Switch / Autonomous Awitch Link ASPM Options: Disabled (Default) / L0s / L1 / L0x & L1 25