Gigabyte MD70-HB1 Manual - Page 74

CPU P State Control

|

View all Gigabyte MD70-HB1 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 74 highlights

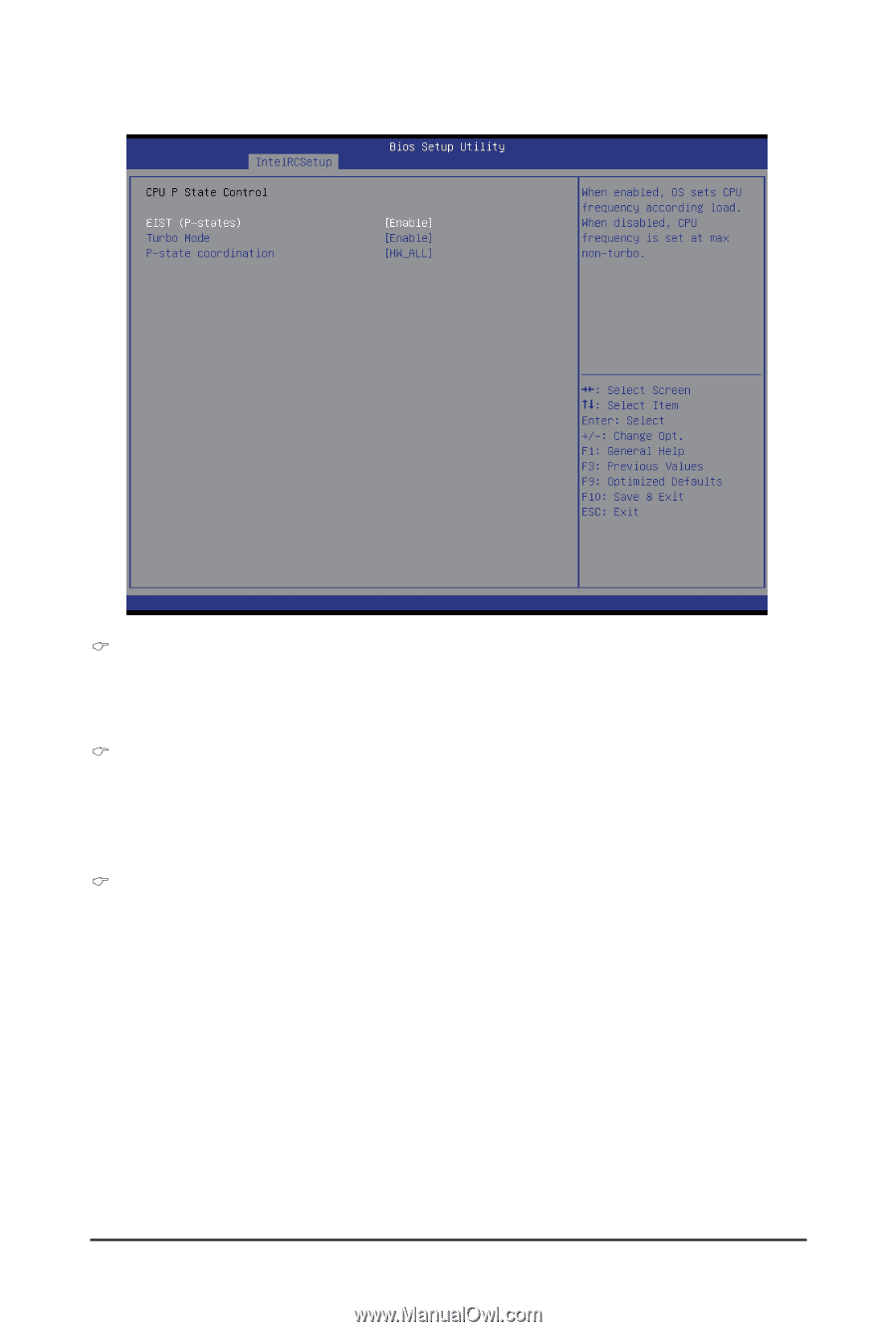

2-3-2-1 CPU P State Control EIST (P-State) Conventional Intel SpeedStep Technology switches both voltage and frequency in tandem between high and low levels in response to processor load. Options available: Enabled/Disabled. Default setting is Enabled. Turbo Mode When this item is enabled, tje processor will automatically ramp up the clock speed of 1-2 of its processing cores to improve its performance. When this item is disabled, the processor will not overclock any of its core. Options available: Enabled/Disabled. Default setting is Enabled. P-state coordination In HW_ALL mode, the processor hardware is responsible for coordinating the P-state among logical processors dependencies. The OS is responsible for keeping the P-state request up to date on all logical processors. In SW_ALL mode, the OS Power Manager is responsible for coordinating the P-state among logical processors with dependencies and must initiate the transition on all of those Logical Processors. In SW_ANY mode, the OS Power Manager is responsible for coordinating the P-state among logical processors with dependencies and may initiate the transition on any of those Logical Processors. Options available: HW_ALL/SW_ALL/SW_ANY. Default setting is HW_ALL. - 74 - BIOS Setup