Gigabyte MNIC8CI Manual - Page 17

KB_MS2 PS/2 Cable Header, LVDS LVDS Headers

|

View all Gigabyte MNIC8CI manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 17 highlights

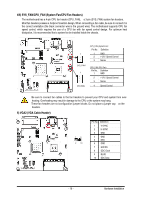

7) KB_MS2 (PS/2 Cable Header) Pin No. Definition 1 GND 2 KDAT 3 F_KDAT 4 KCLK 1 6 5 F_KCLK 6 5V 8) LVDS (LVDS Headers) LVDS stands for Low-voltage differential signaling, which uses high-speed analog circuit techniques to provide multi gigabit data transfers on copper interconnects and is a generic interface standard for high-speed data transmission. 2 30 1 29 1 GND 2 NC 3 EDID Data 4 GND 5 EDID Clock 6 NC 7 GND 8 NC 9 Data0+ 10 NC 11 Data012 Backlight Enable 13 GND 14 Backlight Controller 15 Data1+ 16 GND 17 Data118 GND 19 GND 20 Backlight 5V 21 LVDS Clock22 Backlight 5V 23 LVDS Clock+ 24 Backlight 5V 25 GND 26 GND 27 Data228 LVDS Power 3.3V 29 Data2+ 30 LVDS Power 3.3V - 17 - Hardware Installation

7) KB_MS2 (PS/2 Cable Header)

Pin No.

Definition

1

GND

2

KDAT

3

F_KDAT

4

KCLK

1

6

5

F_KCLK

6

5V

8)

LVDS (LVDS Headers)

LVDS stands for Low-voltage differential signaling, which uses high-speed analog circuit

techniques to provide multi gigabit data transfers on copper interconnects and is a generic interface

standard for high-speed data transmission.

2

30

1

29

1

GND

16

GND

2

NC

17

Data1-

3

EDID Data

18

GND

4

GND

19

GND

5

EDID Clock

20

Backlight 5V

6

NC

21

LVDS Clock-

7

GND

22

Backlight 5V

8

NC

23

LVDS Clock+

9

Data0+

24

Backlight 5V

10

NC

25

GND

11

Data0-

26

GND

12

Backlight Enable

27

Data2-

13

GND

28

LVDS Power 3.3V

14

Backlight Controller

29

Data2+

15

Data1+

30

LVDS Power 3.3V

- 17 -

Hardware Installation