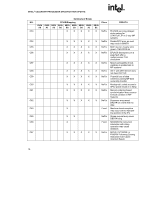

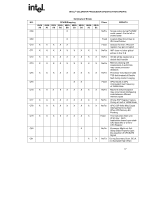

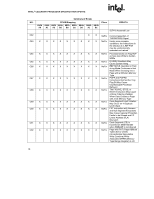

Intel SL3VS Specification Update - Page 29

INTEL, CELERON® PROCESSOR SPECIFICATION UPDATE, Summary of Documentation Changes, CPUID/Stepping,

|

View all Intel SL3VS manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 29 highlights

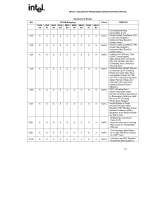

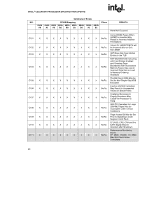

INTEL® CELERON® PROCESSOR SPECIFICATION UPDATE * Fix will be only on Celeron processors with CPUID=068xh. Summary of Documentation Changes CPUID/Stepping 650h 651h 660h 665h 683h 686h 68Ah 6B1h 6B4h NO. A0 A1 A0 B0 B0 C0 D0 A1 B1 Plans DOCUMENTATION CHANGES C1 X X X X X X X X X Doc SSE and SSE2 Instructions Opcodes C2 X X X X X X X X X Doc Executing the SSE2 Variant on a Non-SSE2 Capable Processor C3 X X X X X X X X X Doc Direction Flag (DF) Mistakenly Denoted as a System Flag C4 X X X X X X X X X Doc Fopcode Compatibility Mode C5 X X X X X X X X X Doc FCOS, FPTAN, FSIN, and FSINCOS Trigonometric Domain not correct C6 X X X X X X X X X Doc Incorrect Description of stack C7 X X X X X X X X X Doc EFLAGS Register Correction C8 X X X X X X X X X Doc PSE-36 Paging Mechanism C9 X X X X X X X X X Doc 0x33 Opcode C10 X X X X X X X X X Doc Incorrect Information for SLDT C11 X X X X X X X X X Doc LGDT/LIDT Instruction Information Correction C12 X X X X X X X X X Doc Errors In Instruction Set Reference C13 X X X X X X X X X Doc RSM Instruction Set Summary C14 X X X X X X X X X Doc Correct MOVAPS and MOVAPD Operand Section C15 X X X X X X X X X Doc DAA-Decimal Adjust AL after Addition C16 X X X X X X X X X Doc DAS-Decimal Adjust AL after Subtraction C17 X X X X X X X X X Doc Omission of Dependency between BTM and LBR C18 X X X X X X X X X Doc I/O Permissions Bitmap Base Addy > 0xDFFF Does not Cause #GP(0) Fault C19 X X X X X X X X X Doc Wrong Field Width for MINSS and MAXSS C20 X X X X X X X X X Doc Figure 15-12 PEBS Record Format C21 X X X X X X X X X Doc I/O Permission Bit Map 21