LG KE600 Service Manual - Page 54

General Features, 16.2 Micro-Controller- Micro-Controller Memory, 16.4 Interfaces

|

View all LG KE600 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 54 highlights

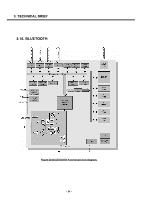

3. TECHNICAL BRIEF 3.16.1. General Features • Single Chip Bluetooth device for cellular applications integrating radio, baseband and memory • Fabricated in advanced low power 0.13•Ïm CMOS technology • Very low component count (6 external components) • Ultra low power design - Peak current 40mA for basic data rate - Peak current 45mA for enhanced data rate - Bluetooth low power mode typ. 25µA • Multiple input clock signals supported (10-40MHz) • Supply from external voltage regulator 1.8V..3.6V 1) • Autonomous power down scenarios of Bluetooth and cellular system supported • Packages: - P-VQFN-48 package - P-WFLGA-56 package • Temperature range from -40°C up to 85°C • Boundary scan for interface lines via JTAG 3.16.2 Micro-Controller-Section • ARM7TDMI-STM ARM® Processor for protocol and application software • Timers + Watchdog + Interrupt Module 3.16.3 Micro-Controller Memory • 32 KByte RAM • 256 KByte read only Program Memory • 8 KByte Patch RAM 3.16.4 Interfaces • UART (Bluetooth - Interface, support for HCI UART and Three-Wire UART transport layers with/without hardware handshaking) up to 3.25MBaud • Two channel PCM Audio interface with I2S mode • I2C Interface • Three channel full duplex CVSD trans coder • General Purpose I/Os - External interrupt - Port output levels available during low-power mode (VDD supplied) • Separate voltage domains for GPIO, UART and PCM interfaces • Control signal for requesting external (cellular) system clock • Multi frequency (e.g. 32.768 kHz) low power clock input - 55 -