MSI P35 NEO COMBO-F User Guide - Page 54

MS-7365 Mainboard, Intel EIST, Adjust CPU FSB Frequency, Advance DRAM Configuration, Con DRAM - manual

|

UPC - 816909039276

View all MSI P35 NEO COMBO-F manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 54 highlights

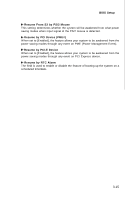

MS-7365 Mainboard [Sergeant 3%] 2nd level of overclocking, increasing the frequency by 3%. [Captain 5%] 3rd level of overclocking, increasing the frequency by 5%. [Colonel 7%] 4th level of overclocking, increasing the frequency by 7%. [General 10%] 5th level of overclocking, increasing the frequency by 10%. [Commander 15%]6th level of overclocking, increasing the frequency by 15%. Important Even though the Dynamic Overclocking Technology is more stable than manual overclocking, basically, it is still risky. We suggest user to make sure that your CPU can afford to overclocking regularly first. If you find the PC appears to be unstable or reboot incidentally, it's better to disable the Dynamic Overclocking or to lower the level of overclocking options. By the way, if you need to conduct overclocking manually, you also need to disable the Dynamic OverClocking first. Intel EIST The Enhanced Intel SpeedStep technology allows you to set the performance level of the microprocessor whether the computer is running on battery or AC power. This field will appear after you installed the CPU which support speedstep technology. Adjust CPU FSB Frequency This item allows you to select the CPU Front Side Bus clock frequency (in MHz). Advance DRAM Configuration Press to enter the sub-menu and the following screen appears. Configure DRAM Timing by SPD Selects whether DRAM timing is controlled by the SPD (Serial Presence Detect) EEPROM on the DRAM module. Setting to [Auto By SPD] enables DRAM timings and the following related items to be determined by BIOS based on the configurations on the SPD. Selecting [Manual] allows users to configure the DRAM timings and the following related items manually. DRAM CAS# Latency This controls the CAS latency, which determines the timing delay (in clock cycles) before SDRAM starts a read command after receiving it. 3-20