Sony STR-K7100 Service Manual - Page 49

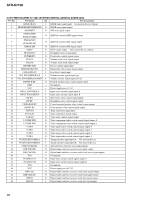

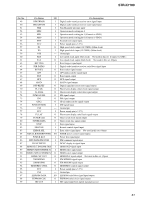

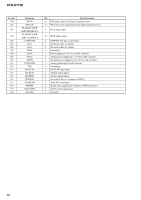

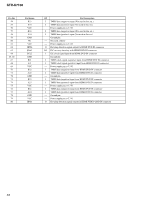

Pin No., Pin Name, Pin Description

|

View all Sony STR-K7100 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 49 highlights

STR-K7100 Pin No. 57 58 59 60 61 62, 63 64 to 66 67 68 69 70 71 72 to 75 76 77 to 80 81 82 83 to 85 86 87 88 89 90 91 92 to 97 98, 99 100 101 102 to 105 106 107, 108 109, 110 111 112 113 114, 115 116 117 118 119 120 Pin Name MOD1 MOD0 EXLOCK VDDI VSS A17, A16 A15 to A13 GP10 GP9 GP8 VDDI VSS D15/GP7 to D12/GP4 VDDE D11/GP3 to D8/GP0 VSS A9 A12 to A10 TDO TMS XTRST TCK TDI VSS A8 to A3 D7, D6 VDDI VSS D5 to D2 VDDE D1, D0 A2, A1 VSS A0 PM SDI3, SDI4 SYNC TST2 GP11 TST3 VDDI I/O Pin Description I Operation mode signal input (L: 386fs, H: 256fs) (Fixed at H.) I Operation mode signal input (L: single chip mode, H: use prohibited) (Fixed at L.) I Error detection signal input from digital audio interface receiver IC I Power supply pin (+1.9 V) - Ground pin O Not used. (Open) O External memory address signal output for SDRAM IC O Not used. (Open) O GP9 signal output for system control IC I Audio signal input from digital audio interface receiver IC I Power supply pin (+1.9 V) - Ground pin I/O External memory data input/output for SDRAM IC I Power supply pin (+3.3 V) I/O External memory data input/output for SDRAM IC - Ground pin O External memory address signal output for SDRAM IC O External memory address signal output for SDRAM IC O Not used. (Fixed at H.) I Not used. (Fixed at H.) I Not used. (Fixed at H.) I Not used. (Fixed at H.) I Not used. (Fixed at H.) - Ground pin O External memory address signal output for SDRAM IC I/O External memory data input/output for SDRAM IC I Power supply pin (+1.9 V) - Ground pin I/O External memory data input/output for SDRAM IC I Power supply pin (+3.3 V) I/O External memory data input/output for SDRAM IC O External memory address signal output for SDRAM IC - Ground pin O External memory address signal output for SDRAM IC I PLL initialization signal input from system control IC I Not used. (Open) I Sync/async select signal input (L: sync, H: async) (Fixed at H.) I Not used. (Connect to ground.) I Not used. (Connect to ground.) I Not used. (Connect to ground.) I Power supply pin (+1.9 V) 49