Compaq ProLiant 1000 Memory technology evolution: an overview of system memory - Page 10

Memory channel interleaving

|

View all Compaq ProLiant 1000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 10 highlights

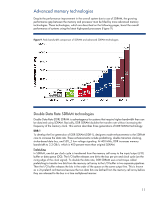

Memory channel interleaving Multi-core processors running multi-threaded applications pose a significant challenge to the memory subsystem. The processor cores share the bandwidth of the memory bus; therefore, the multi-core processor's performance is limited by the memory bus bandwidth. Even with sufficient memory bus bandwidth, the actual throughput of a single memory controller can create a bottleneck as it handles memory requests from multiple cores. To overcome this bottleneck, manufacturers are designing memory controller chips with multiple integrated memory controllers (Figure 8). The chip can contain two, three, or four memory controllers that operate independently of each other to access up to two DIMMs per channel. This enables a process called channel interleaving. In channel interleaving, each integrated memory controller successively provides a 64-byte cache line of data from the first DIMM on its channel. After the last memory controller completes the data transfer, the memory controllers can provide a cache line from a second DIMM on each channel. Channel interleaving does not prevent bank or rank interleaving. The effective throughput of the memory controller is the sum of the individual memory channels. As the number of cores on a single processor increases, the number of integrated memory controllers will need to increase accordingly to provide the necessary throughput. Figure 8. Memory channel interleaving using multiple integrated memory controllers 10