HP ProLiant BL660c HP Power Regulator for ProLiant servers - Page 4

HP Dynamic Power Savings mode, Measuring CPU utilization, Processor granularity

|

View all HP ProLiant BL660c manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 4 highlights

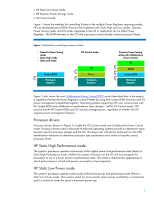

HP Dynamic Power Savings mode The Dynamic Power Savings mode is similar in concept to Intel's Demand Based Switching with SpeedStep Technology and to AMD's PowerNow!™, but it adds a significant HP innovation. Power Regulator uses an HP ROM-based algorithm to monitor processor activity. It adjusts processor performance states to match performance levels to application load. In Dynamic Power Savings mode, Power Regulator determines the amount of time each logical processor in the system spends in the operating system's idle loop. In the simplest case, where only two P-states are available, the logic is straightforward. It evaluates the following ratio where clocks per unit time is the frequency: clocks performing useful work total clocks available in Pmax When the ratio is high (more time spent in the idle loop), the algorithm sets the processor to Pmin. When the algorithm detects a low ratio-indicating a high application load-Power Regulator switches the processor in real time to Pmax. Beginning with G6 servers, Power Regulator Dynamic Power Savings mode takes advantage of all available processor P-states. In this case, the algorithm is more complicated than a simple ratio. The result is that Power Regulator will find the optimal performance state based on accurate use of Pmax and Pmin and every P-state in between. HP ProLiant servers enable HP Dynamic Power Savings mode by default to provide significant, out-ofthe-box power savings. And, it does this without significantly affecting system performance. Measuring CPU utilization Power-state decisions made in Dynamic Power Savings mode take into account all processor activity (kernel-mode and user-mode). Power Regulator determines CPU utilization by reading a performance event counter residing within the processor. The event counter collects non-halted clock cycles. Modern operating systems execute a HLT instruction when a processor is idle, preventing the processor from running in an idle loop while searching for work. Processor granularity The ROM-based dynamic power algorithm executes on every logical processor and hyperthread in the physical processor package. This means every core in a multi-core physical processor package. The power algorithm requests the higher P-state only for logical processors that require it. It tells the processor hardware to set the P-state of each logical processor based on that logical processor's current utilization. Architectural dependencies within the physical processor may require some or all logical processors within the processor package to be set at the same P-state. When an architectural dependency is present, we allow the processor package (hardware processor management) to manage those issues. The processor package will never choose a P-state lower than the performance requirement of any logical processor in the package. Dynamic Power Savings mode response times Starting with ProLiant G6 servers, you are able to choose between Dynamic Power Savings mode response times (slow and fast). Power Regulator Dynamic Power Savings mode switches between P-states when the logic identifies an increase or a decrease in performance requirements. The switch occurs during a specific, user-selectable time interval. Slow and fast response times describe the fixed time interval during which the logic can identify a change in performance requirements. Slow response times (15 seconds) are typically more power efficient, but they increase latencies and slow performance reaction to a load increase. Fast response times (0.125 seconds) react to load increases more quickly and reduce performance latencies, but often at the cost of power efficiency. 4