Intel DH55TC DH55TC Technical Product Specification - Page 15

Intel, H55 Express Chipset, System Memory - ddr3

|

View all Intel DH55TC manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 15 highlights

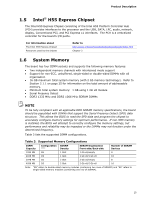

Product Description 1.5 Intel® H55 Express Chipset The Intel H55 Express Chipset consisting of the Intel H55 Platform Controller Hub (PCH) provides interfaces to the processor and the USB, SATA, LPC, audio, network, display, Conventional PCI, and PCI Express x1 interfaces. The PCH is a centralized controller for the board's I/O paths. For information about The Intel H55 Express Chipset Resources used by the chipset Refer to http://www.intel.com/products/desktop/chipsets/index.htm Chapter 2 1.6 System Memory The board has four DIMM sockets and supports the following memory features: • Two independent memory channels with interleaved mode support • Support for non-ECC, unbuffered, single-sided or double-sided DIMMs with x8 organization • 16 GB maximum total system memory (with 2 Gb memory technology). Refer to Section 2.1.1 on page 35 for information on the total amount of addressable memory. • Minimum total system memory: 1 GB using 1 Gb x8 module • Serial Presence Detect • DDR3 1333 MHz and DDR3 1066 MHz SDRAM DIMMs NOTE To be fully compliant with all applicable DDR SDRAM memory specifications, the board should be populated with DIMMs that support the Serial Presence Detect (SPD) data structure. This allows the BIOS to read the SPD data and program the chipset to accurately configure memory settings for optimum performance. If non-SPD memory is installed, the BIOS will attempt to correctly configure the memory settings, but performance and reliability may be impacted or the DIMMs may not function under the determined frequency. Table 3 lists the supported DIMM configurations. Table 3. Supported Memory Configurations DIMM Capacity Configuration (Note) SDRAM Density SDRAM Organization Front-side/Back-side Number of SDRAM Devices 1024 MB SS 1 Gbit 1 Gb x8/empty 8 2048 MB DS 2048 MB SS 4096 MB DS 1 Gbit 1 Gb x8/1 Gb x8 16 2 Gbit 2 Gb x8/empty 8 2 Gbit 2 Gb x8/2 Gb x8 16 Note: "DS" refers to double-sided memory modules (containing two rows of SDRAM) and "SS" refers to single-sided memory modules (containing one row of SDRAM). 15