Pioneer DVL-909 Service Guide - Page 35

Pd3381a Dvdm Assy : Ic601

|

View all Pioneer DVL-909 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 35 highlights

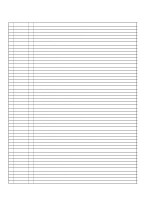

PD3381A (DVDM ASSY : IC601) • System Control CPU • Block Diagram DV-505, DVL-909, DV-S9 PA15/IRQ3/DREQ1 PA14/IRQ2/DACK1 PA13/IRQ1/DREQ0/TCLKB PA12/IRQ0/DACK0/TCLKA PA11/DPH/TIOCB1 PA10/DPL/TIOCA1 PA9/AH/IRQOUT/ADTRG PA8/BREQ PA7/BACK PA6/RD PA5/WRH(LBS) PA4/WRL(WR) PA3/CS7/WAIT PA2/CS6/TIOCB0 PA1/CS5/RA5/RAS PA0/CS4/TIOCA0 CS3/CASL CS2 CS1/CASH CS0 A21 A20 A19 A18 A17 A16 OSCILLATOR ADDRESS RES 79 WDTOVF 78 MD2 82 MD1 81 MD0 80 NMI 76 CK 71 EXTAL 73 XTAL 74 Vpp 77 Vcc 15 Vcc 43 Vcc 70 Vcc 75 Vcc 83 Vcc 84 Vcc 99 Vss 3 Vss 12 Vss 22 Vss 31 Vss 40 Vss 52 Vss 61 Vss 72 Vss 96 Vss 106 AVref 86 AVcc 85 AVss 91 69 68 67 66 65 64 63 62 60 59 58 57 56 55 54 53 PORT A 51 50 49 48 47 46 45 44 42 41 ADDRESS 64k PROM / MASK ROM 4kB RAM1 CPU INTERRUPT USER BREAK CONTROLLER CONTROLLER DIRECT MEMORY ACCESS CONTROLLER BUS STATE CONTROLLER SERIAL COMMUNICATION INTERFACE (×2CHANNEL) PROGRAMABLE TIMING PATTERN CONTROLLER 16BIT INTEGRATED TIMER PULSE UNIT A/D WATCHDOG CONVERTER TIMER PORT C PORT B 95 94 93 92 90 89 88 87 2 1 112 111 110 109 108 107 105 104 103 102 101 100 98 97 DATA/ADDRESS 39 A15 38 A14 37 A13 36 A12 35 A11 34 A10 33 A9 32 A8 30 A7 29 A6 28 A5 27 A4 26 A3 25 A2 24 A1 23 A0(HBS) 21 AD15 20 AD14 19 AD13 18 AD12 17 AD11 16 AD10 14 AD9 13 AD8 11 AD7 10 AD6 9 AD5 8 AD4 7 AD3 6 AD2 5 AD1 4 AD0 PC7/AN7 PC6/AN6 PC5/AN5 PC4/AN4 PC3/AN3 PC2/AN2 PC1/AN1 PC0/AN0 PB15/TP15/IRQ7 PB14/TP14/IREQ6 PB13/TP13/IREQ5/SCK1 PB12/TP12/IREQ4/SCK0 PB11/TP11/TxD1 PB10/TP10/RxD1 PB9/TP9/TxD0 PB8/TP8/RxD0 PB7/TP7/TOCXB4/TCLKC PB6/TP6/TOCXA4/TCLKC PB5/TP5/TIOCB4 PB4/TP4/TIOCA4 PB3/TP3/TIOCB3 PB2/TP2/TIOCA3 PB1/TP1/TIOCB2 PB0/TP0/TIOCA2 Periphery address bus(24 bit) Periphery data bus(16 bit) Internal address bus(24 bit) Internal upper data(16 bit) Internal lower data(16 bit) 35