Seagate ST3500630A Serial ATA - A Comparison with Ultra ATA Technology (57K, P - Page 2

Strobe

|

UPC - 000067575145

View all Seagate ST3500630A manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 2 highlights

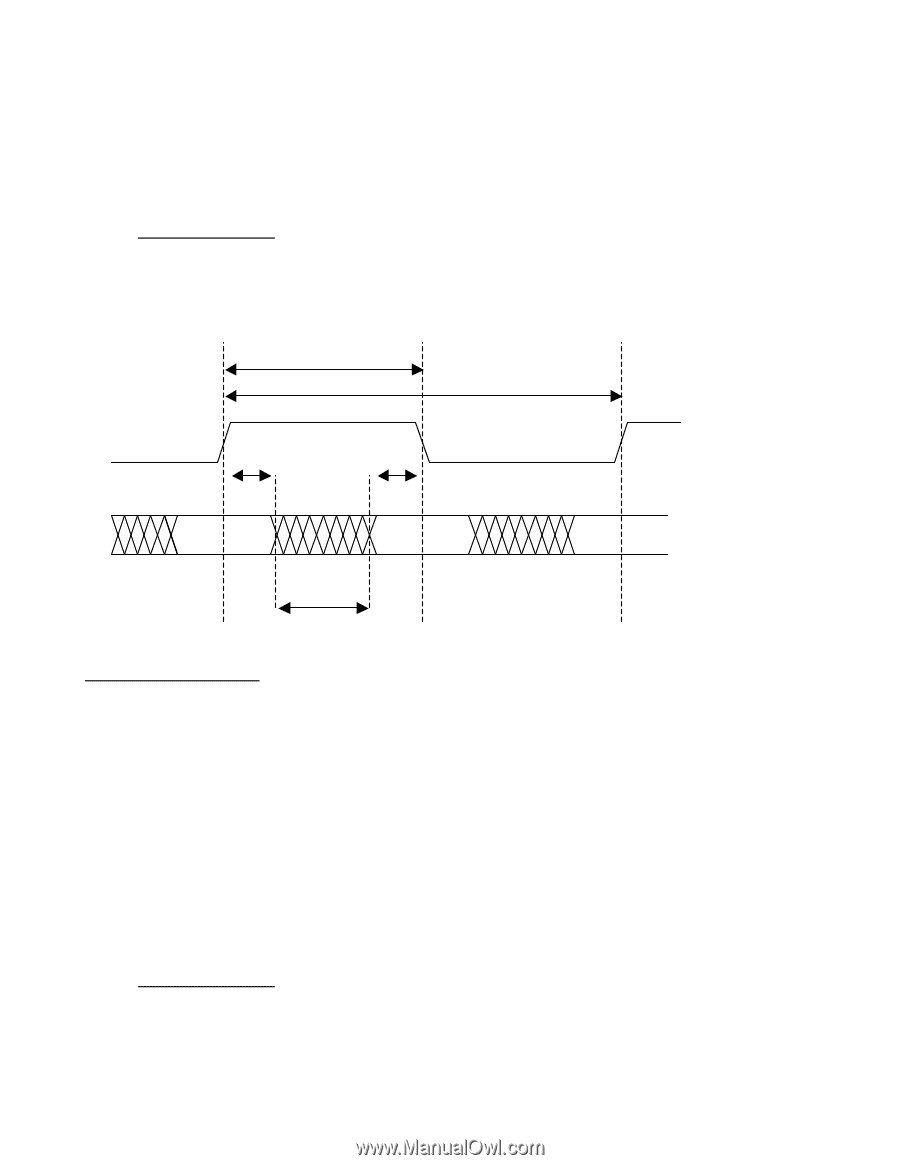

Mbytes/sec, the data bus must be clocked at 50MHz. To minimize strobe design complexity, Ultra ATA uses a "double data rate" or double-edge clocking mechanism for all Ultra DMA transfers. Using this technology, data is registered both on the rising and falling edges of the data strobe, halving the required strobe frequency. Thus the bandwidth is: 25MHz strobe x 2 for double data rate clocking x 16 bits per edge / 8 bits per byte = 100 Mbytes/sec Timing - As mentioned above, data must be clocked at 50MHz, or every 20ns. Note that because of data setup and hold times, all data lines must in fact switch and settle within approximately 10ns (see Figure 1). It is this worst case switching time that designers must meet. Strobe ½ Cycle - 20ns Strobe Full Cycle - 40ns Strobe Required Hold Time 4.8ns Required Setup Time 4.8ns Data 10.4ns Max Switching Time Figure 1 - Ultra DMA Burst Transfer Timing Serial ATA Bus Architecture Bus Design - In contrast to Ultra ATA's parallel bus design, Serial ATA uses a single signal path to transmit data serially, or bit by bit, and a second serial path to return receipt acknowledgements to the sender. Because each of these signal paths is a 2-wire differential pair, the Serial ATA bus consists of 4 signal lines per channel. Control information is transmitted either as short predefined bit sequences that are distinguishable from data, in packet format, or using out-of-band signaling (control signals sent using on/off signal pulses, similar to Morse code), and thus does not require separate transmission lines. Bandwidth - The 16-bit wide parallel Ultra ATA bus is capable of transmitting two bytes of data per clock. Though Serial ATA transmits only a single bit per clock, the serial bus may be run at a much higher speed to compensate for the loss of parallelism. Serial ATA will be introduced with a bandwidth of 1500Mbits/sec, or 1.5Gbits/sec. Because data is encoded using 8b/10b encoding (an 80% efficient encoding used with digital differential signaling to maintain a constant average "DC" bias point), the effective maximum throughput is 150Mbytes/sec. 1500MHz embedded clock x 1 bit per clock x 80% for 8b10b encoding / 8 bits per byte = 150 Mbytes/sec Serial ATA : A Comparison with Ultra ATA Technology - 2 -