Acer EL1210 Service Guide - Page 24

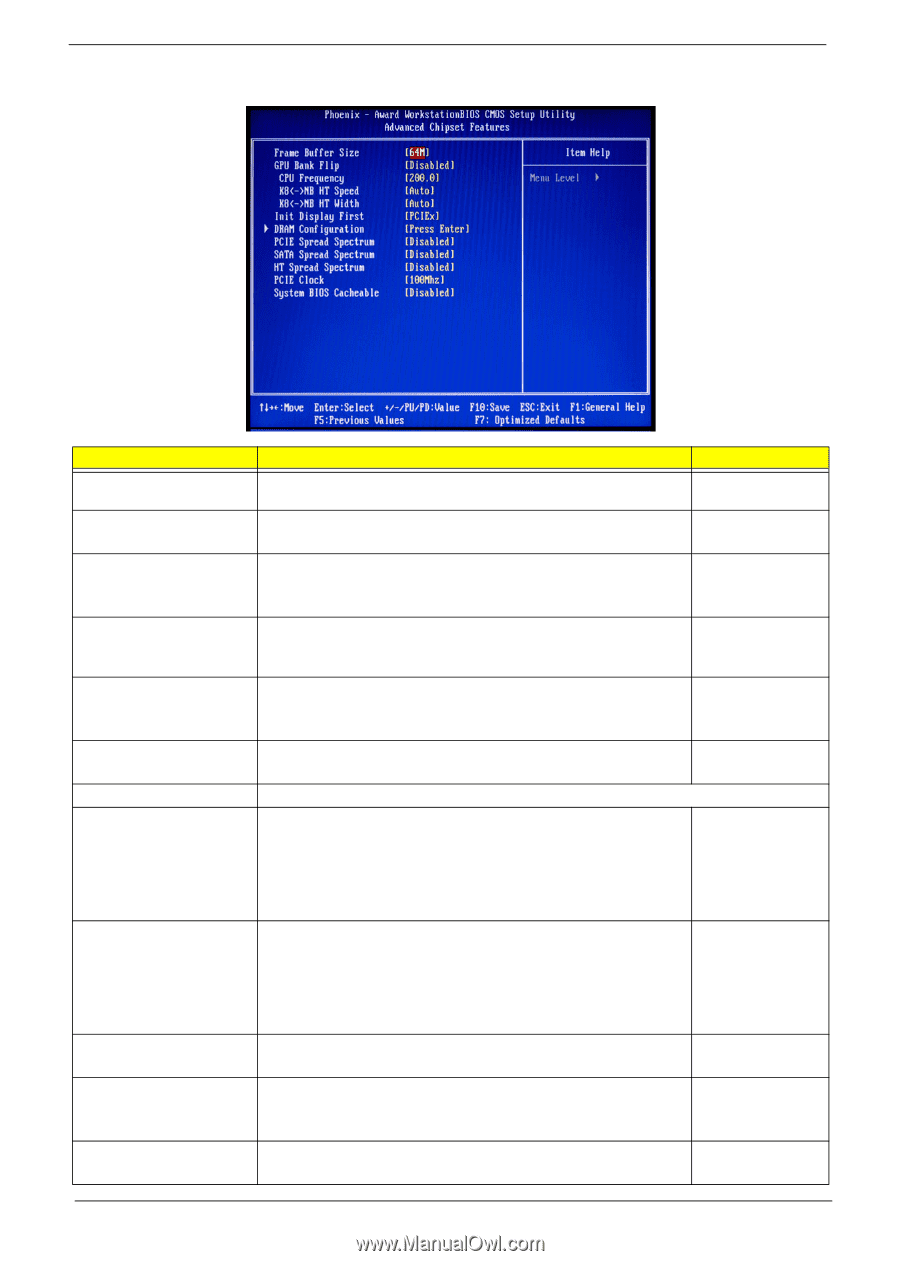

Advanced Chipset Features, Parameter, Description, Option, Disabled, PCIEx, Enter

|

View all Acer EL1210 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 24 highlights

Advanced Chipset Features Parameter Frame Buffer Size GPU Bank Flip CPU Frequency KBNB HT Speed KBNB HT Width Init Display First DRAM Configuration PCIE Spread Spectrum SATA Spread Spectrum HT Spread Spectrum PCIE Clock System BIOS cacheable 16 Description This parameter can be configured if the iGPU Frame Buffer Control is set to Manual. Enables or disables the GPU Bank Flip feature. Sets processor minimum and maximum frequency. Controls the physical speed of the processor to the Northbridge HT link. Controls the processor to the Northbridge link bandwidth. Specifies the first initiation of the monitor display from the installed PCI Express graphics card or the onboard VGA. Press Enter to configure memory timing and operation settings. Allows you to reduce the EMI of the PCI Express bus by modulating the signals it generates so that the spikes are reduced to flatter curves. When set to down spread, the chipset modulates the PCI Express bus' baseline signal downwards by a small amount. When set to disabled, the chipset disables any modulation of the PCI Express bus' baseline signal. Allows you to reduce the EMI of the SATA bus by modulating the signals it generates so that the spikes are reduced to flatter curves. When set to down spread, the chipset modulates the SATA bus' baseline signal downwards by a small amount. When set to disabled, the chipset disables any modulation of the SATA bus' baseline signal. Enables or disables the spread spectrum for Hyper Transport. Sets the PCI Express clock frequency. Enables or disables the caching of the mainboard BIOS ROM from F0000h to FFFFFh by the processor's Level 2 cache. Option 64, 16, 32, 128, 256 MB Disabled Enabled 200 Minimum 100 Maximum 500 Auto 200, 400, 600, 800 MHz, 1 GHz Auto Up 8/16 Down 8/16 PCIEx Onboard Disabled Down Spread Disabled Down Spread Disabled 0.5% H. KissCntr 100 Minimum 100 Maximum 200 Disabled Enabled Chapter 2