Acer EL1210 Service Guide - Page 25

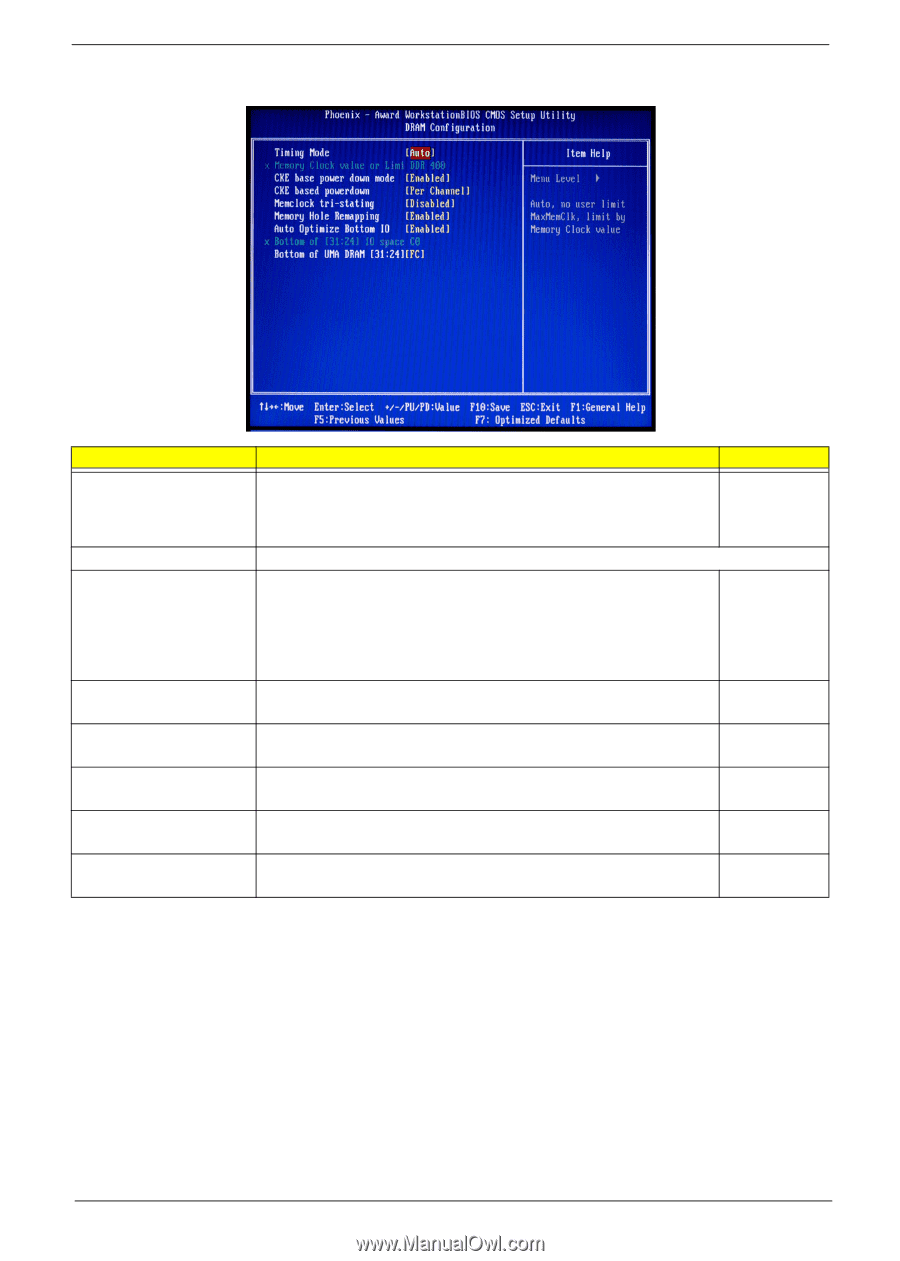

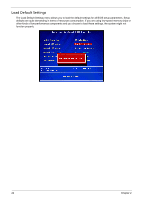

DRAM Configuration, Parameter, Description, Option, Disabled, Per Channel, Enabled, Minimim 0000

|

View all Acer EL1210 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 25 highlights

DRAM Configuration Parameter Timing Mode Memory Clock value or Limit CKE base power down mode CKE based power down Memclock tri-stating Memory Hole Remapping Auto Optimize Bottom IO Bottom of UMA DRAM [31:24] [FC] Description When set to auto mode, the system reads the electronic data sheet of the memory modules and adjusts the timings accordingly. When set to MaxMemClk, you can manually specify the memory clock frequency independent of the system bus frequency. Displays the current memory clock frequency. All synchronous memory devices can go into sleep mode as soon as the clock enable (CKE) signal is disasserted. In that case, the internal clocks are disabled and the memory chip goes into auto-refresh mode which is the lowest power state at which the memory retains data. If then power is turned off, the device will lose all data, however, as long as standby power is maintained, no data loss will occur. Sets the CKE power saving through disasserting clock enable using system level or per channel basis. Enables or disables the memory clock tri-stating during C3 an Alt VD feature. Enables or disables memory remapping around the memory hole. Allows you to auto optimize maximal memory size when kernel assigns PCI Resources. Allows you to enter a HEX number ranging from 0000 to 00F0. Option Auto MaxMemClk Manual Disabled Enabled Per Channel Per CS Disabled Enabled Enabled Disabled Enabled Disabled Minimim 0000 Maximum 00FC Chapter 2 17