Acer R310-U-P3200 User Guide - Page 34

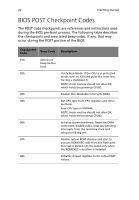

Checkpoint, Beep Code, Description, Memory to memory disabled - ram

|

UPC - 750519118634

View all Acer R310-U-P3200 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 34 highlights

24 3 Getting Started Checkpoint Code Beep Code 14h 16h 1-2-2-3 17h 18h 1Ah Description Verify that the 8742 keyboard controller is responding. Send a self-test command to the 8742 and wait for results. Also read the switch inputs from the 8742 and write the keyboard controller command byte. Verify that the ROM BIOS checksums to zero. Initialize external cache before autosizing memory. Initialize all three of the 8254 timers. Set the clock timer (0) to binary count, mode 3 (square wave mode), and read/write LSB then MSB. Initialize the clock timer to zero. Set the RAM refresh timer (1) to binary count, mode 2 (Rate Generator), and read/ write LSB only. Set the counter to 12H to generate the refresh at the proper rate. Set sound timer (2) to binary count, mode 3, and read/write LSB, then MSB. Initialize DMA command register with these settings: 1. Memory to memory disabled 2. Channel 0 hold address disabled 3. Controller enabled 4. Normal timing 5. Fixed priority 6. Late write selection 7. DREQ sense active 8. DACK sense active low Initialize all 8 DMA channels with these settings: 1. Single mode 2. Address increment 3. Auto initialization disabled (channel 4 Cascade) 4. Verify transfer