HP DL165 Technologies for HP ProLiant 100-series G5 (Generation 5) servers, 2n - Page 3

Xeon quad-core processors, architecture using two dual-core processors

|

UPC - 884962026601

View all HP DL165 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 3 highlights

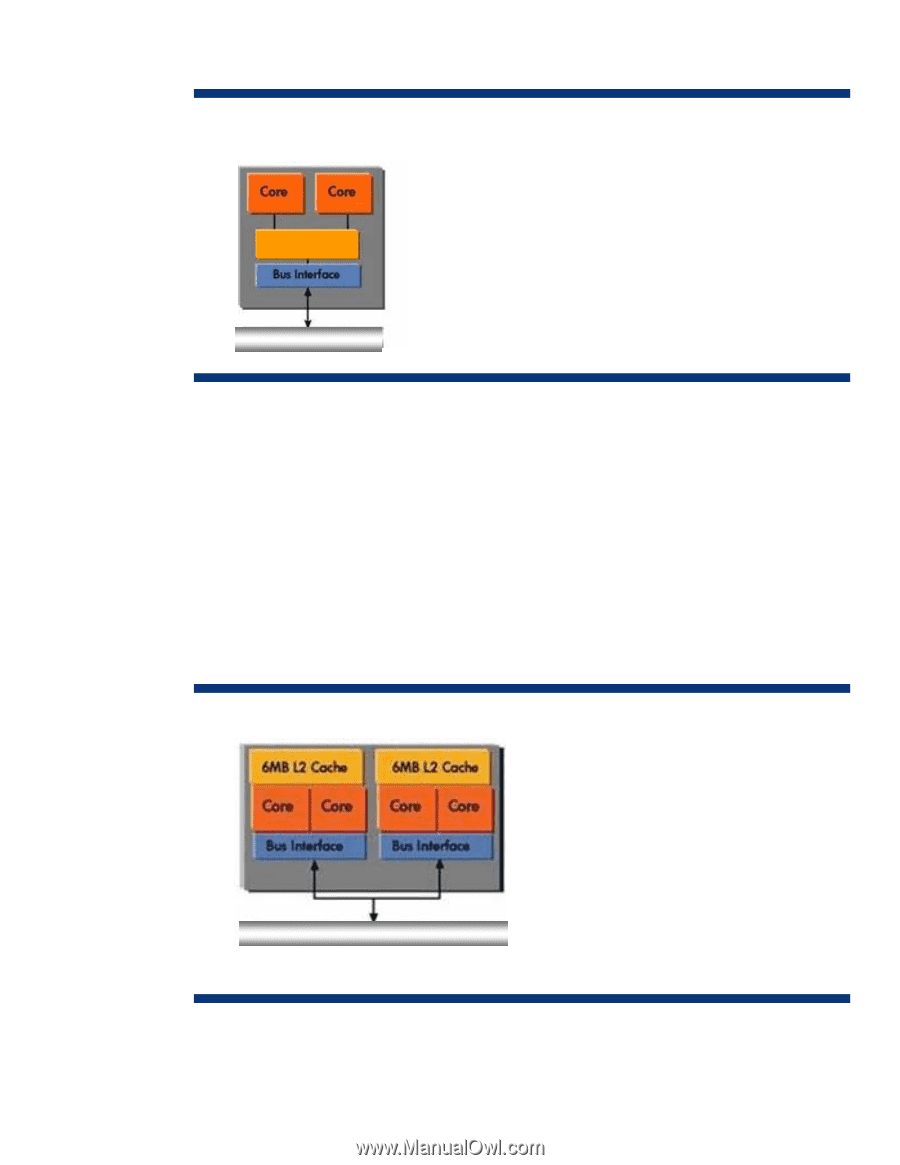

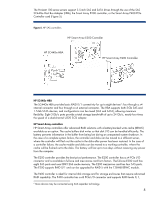

Figure 1. Block diagram of dual-core Intel Xeon 3100 and 5200 sequence processors L2 Cache Xeon 3100: 6-MB L2 cache and 1333-MHz FSB Xeon 5200: 6-MB L2 cache and 1066-/1333-/1666-MHz FSB ProLiant servers supporting the Xeon 3100 sequence processors use the Intel 3200 series chipset while Xeon 5000-based servers use the Intel 5000 chipset. These chipsets support Error Correction Code (ECC) memory for a high level of data integrity, reliability, and system uptime. ECC can detect multiple-bit memory errors and locate and correct single-bit errors to keep business applications running smoothly. Xeon quad-core processors The quad-core Intel Xeon 3300 and 5400 series processors use 45-nm technology and an architecture using two dual-core processors, each with a 6-MB L2 cache (Figure 2). Each core pair shares a 6-MB L2 cache, and each of the two cores can access the full 6 MB if necessary. Xeon 3300 series processors support an FSB speed of 1333 MHz. Xeon 5400 series processors support 1333- or 1666-MHz FSB operation. Xeon-based ProLiant 100-series servers employing Xeon 3300 or 5400 processors use Intel 5000 series chipsets that support dual independent buses, DDR2 DIMMs, and PCI Express I/O slots. Figure 2. Block diagram of quad-core Intel Xeon 3300 and 5400 sequence processor Xeon 3300: 1333-MHz FSB Xeon 5400: 1333-/1666-MHz FSB FSB 3