HP Vectra VEi8 HP Vectra VEi7, VEi8 & VLi8, Technical Reference Manual (V - Page 9

Intel Pentium III, GTL+ Technology, Pentium Processor Packages - motherboard driver

|

View all HP Vectra VEi8 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 9 highlights

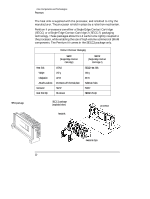

Core Components and Technologies Processors Intel Pentium III The Pentium III processor uses the same basic core and L2 cache as the Pentium II. In addition to this, however, it uses 70 new multimediaoriented instructions known as SSE (streaming SIMD extensions). These SIMD (single instruction multiple data) instructions enable the CPU to perform simultaneous floating point calculations on multiple data. This brings substantial improvements to 3D graphics, video encoding and decoding and other floating point-intensive operations that operate on large sets of data such as voice recognition. Like the Pentium II, the Pentium III processor connects to the motherboard by a Slot 1 connector. It comes in a SECC 2 package only (see "Pentium Processor Packages" below). GTL+ Technology The Processor-Local (PL) bus of Socket 370 Celeron, Pentium II and Pentium III processors, also referred to as their FSB (Front Side Bus), is implemented in GTL+ technology. This technology features opendrain signal drivers that are pulled-up to 1.5 V through 56 ohm resistors on the bus, acting as bus terminators. The supported operating frequencies of the GTL+ bus are 66 or 100 MHz. The width of the data bus is 64 bits, the width of the address is 32 bits. The control signals of the PL bus allows the implementation of a "split -transaction" bus protocol. This allows the processor to send its request (such as asking for the contents of a given memory address) and then to release the bus, rather than waiting for the result, thereby allowing the bus to accept another request. The target device (PCI AGP controller chip) then requests the bus again when it is ready to respond, and sends the requested data packet. Up to four transactions can be outstanding at any given time. Pentium Processor Packages The processor and level-2 cache memory are packaged in a selfcontained, pre-sealed module, installed in a Slot 1 socket on the system board. 9