Intel D955XCS Product Guide - Page 65

A Error Messages and Indicators - thermal module

|

UPC - 735858173841

View all Intel D955XCS manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 65 highlights

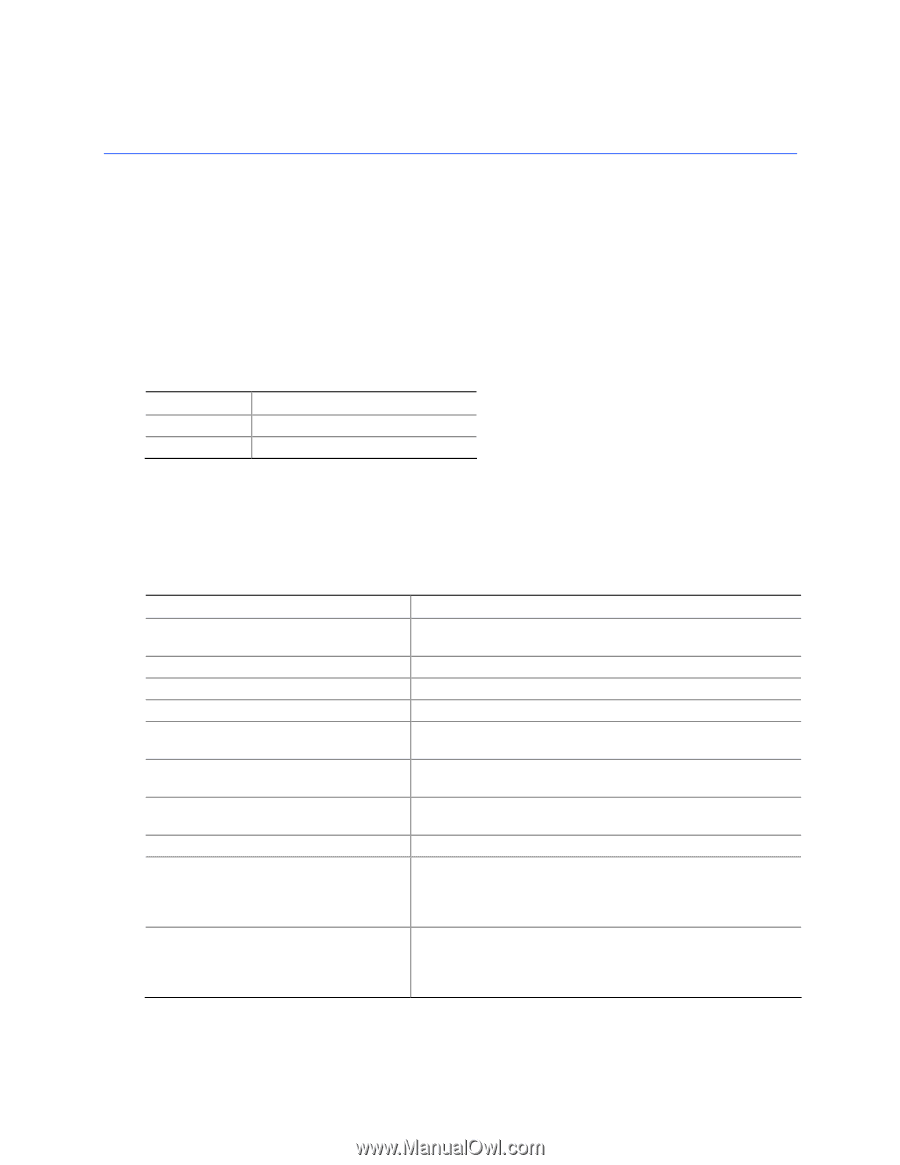

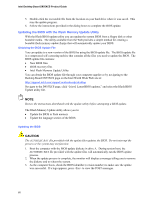

A Error Messages and Indicators Desktop Board D955XCS reports POST errors in two ways: • By sounding a beep code • By displaying an error message on the monitor BIOS Beep Codes The BIOS beep codes are listed in Table 11. The BIOS also issues a beep code (one long tone followed by two short tones) during POST if the video configuration fails (a faulty video card or no card installed) or if an external ROM module does not properly checksum to zero. Table 11. Beep Codes Beep 3 Siren Description No memory CPU overheat (on reboot) BIOS Error Messages When a recoverable error occurs during the POST, the BIOS displays an error message describing the problem. Table 12. BIOS Error Messages Error Message PROCESSOR_THERMAL_TRIP_ERROR MULTI_BIT_ECC_ERROR SINGLE_BIT_ECC_ERROR CMOS_BATTERY_ERROR CMOS_CHECKSUM_ERROR CMOS_TIMER_ERROR MEMORY_SIZE_DECREASE_ERROR INTRUDER_DETECTION_ERROR SPD_TOLER_ERROR MEM_OPTIMAL_ERROR Explanation CPU was previously shutdown due to a thermal event (overheating). The firmware has detected that a Multi-Bit ECC Error occurred. The firmware has detected that a Single-Bit ECC Error occurred. The firmware has detected that a CMOS battery failure occurred. The firmware has detected that a CMOS Checksum Error occurred. The firmware has detected that the system date/time has not been set. The firmware has detected that the system memory has decreased. The system chassis was opened. SERIAL PRESENCE DETECT (SPD) device data missing or inconclusive. Properly programmed SPD device data is required for reliable operation. DDR2 533 MHz memory assumed at slowest timings. The installed amount of memory in Channel A is not equal to the amount of memory in Channel B. Maximum memory performance is achieved with equal amounts of memory installed in each channel. 65