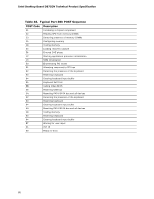

Intel DB75EN Technical Product Specification - Page 76

Table 47., Port 80h POST Codes

|

View all Intel DB75EN manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 76 highlights

Intel Desktop Board DB75EN Technical Product Specification Table 47. Port 80h POST Codes Port 80 Code Progress Code Enumeration 0x00,0x01,0x02,0x03,0x04,0x05 ACPI S States Entering S0, S2, S3, S4, or S5 state 0x10,0x20,0x30,0x40,0x50 Resuming from S2, S3, S4, S5 Security Phase (SEC) 0x08 Starting BIOS execution after CPU BIST 0x09 SPI prefetching and caching 0x0A Load BSP microcode 0x0B Load APs microcodes 0x0C Platform program baseaddresses 0x0D Wake Up All APs 0x0E Initialize NEM 0x0F Pass entry point of the PEI core 0x11 0x12 0x13 0x14 PEI before MRC PEI Platform driver Set bootmode, GPIO init Early chipset register programming including graphics init Basic PCH init, discrete device init (1394, SATA) LAN init 0x15 Exit early platform init driver PEI SMBUS 0x16 SMBUSriver init 0x17 Entry to SMBUS execute read/write 0x18 Exit SMBUS execute read/write PEI CK505 Clock Programming 0x19 Entry to CK505 programming 0x1A 0x1B Exit CK505 programming PEI Over-Clock Programming Entry to entry to PEI over-clock programming 0x1C 0x21 Exit PEI over-clock programming Memory MRC entry point 0x23 Reading SPD from memory DIMMs 0x24 0x27 Detecting presence of memory DIMMs Configuring memory 0x28 Testing memory 0x29 Exit MRC driver continued 76