Intel E3300 Data Sheet - Page 90

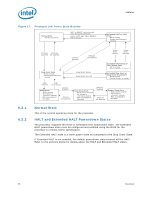

Processor Power Status Indicator PSI Signal

|

View all Intel E3300 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 90 highlights

Features 6.2.7 6.2.8 6.3 Deeper Sleep State The Deeper Sleep state is similar to the Deep Sleep state but the core voltage is reduced to a lower level. The Deeper Sleep state is entered through assertion of the DPRSTP# pin while in the Deep Sleep state. Exit from Deeper Sleep is initiated by DPRSTP# de-assertion. PECI is not available and will not respond while in the Deeper Sleep State. Refer to the appropriate Thermal and Mechanical Design Guidelines (see Section 1.2) for guidance on how to ensure PECI thermal data is available when the Deeper Sleep State is enabled. In response to entering Deeper Sleep, the processor drives the VID code corresponding to the Deeper Sleep core voltage on the VID pins. Unlike typical Dynamic VID changes (where the steps are single VID steps) the processor will perform a VID jump on the order of 100 mV. To support the Deeper Sleep State the platform must use a VRD 11.1 compliant solution. Enhanced Intel SpeedStep® Technology The processor supports Enhanced Intel SpeedStep Technology. This technology enables the processor to switch between frequency and voltage points that may result in platform power savings. To support this technology, the system must support dynamic VID transitions. Switching between voltage/frequency states is software controlled. Enhanced Intel SpeedStep Technology is a technology that creates processor performance states (P states). P states are power consumption and capability states within the Normal state as shown in Figure 17. Enhanced Intel SpeedStep Technology enables real-time dynamic switching between frequency and voltage points. It alters the performance of the processor by changing the bus to core frequency ratio and voltage. This allows the processor to run at different core frequencies and voltages to best serve the performance and power requirements of the processor and system. Note that the front side bus is not altered; only the internal core frequency is changed. To run at reduced power consumption, the voltage is altered in step with the bus ratio. The following are key features of Enhanced Intel SpeedStep Technology: • Voltage/Frequency selection is software controlled by writing to processor MSR's (Model Specific Registers), thus eliminating chipset dependency. - If the target frequency is higher than the current frequency, Vcc is incriminated in steps (+12.5 mV) by placing a new value on the VID signals after which the processor shifts to the new frequency. Note that the top frequency for the processor can not be exceeded. - If the target frequency is lower than the current frequency, the processor shifts to the new frequency and Vcc is then decremented in steps (-12.5 mV) by changing the target VID through the VID signals. Processor Power Status Indicator (PSI) Signal The processor incorporates the PSI# signal that is asserted when the processor is in a reduced power consumption state. PSI# can be used to improve efficiency of the voltage regulator, resulting in platform power savings. PSI# may be asserted only when the processor is in the Deeper Sleep state. § 90 Datasheet