Philips LC3141 Service Manual - Page 8

D5-6-7 - 40

|

View all Philips LC3141 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 8 highlights

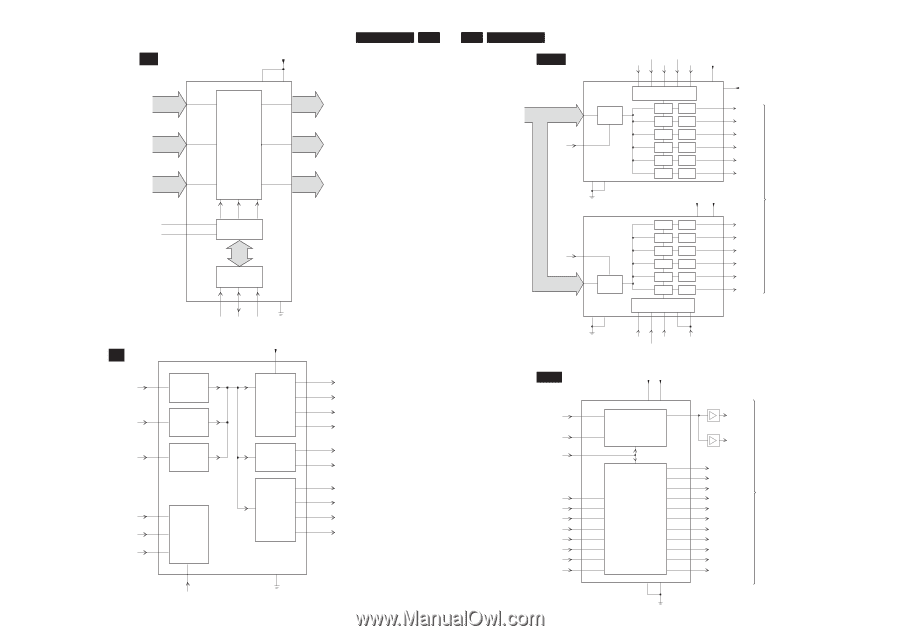

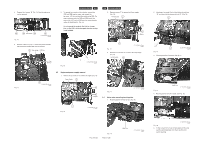

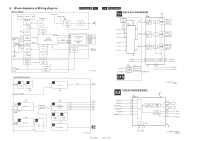

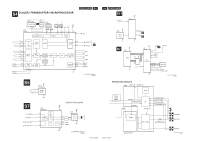

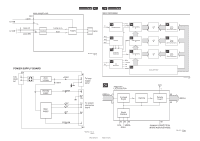

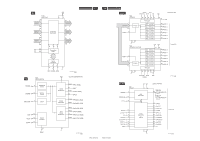

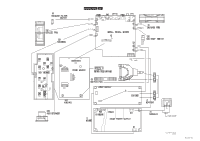

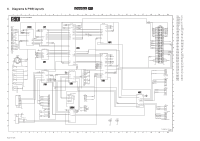

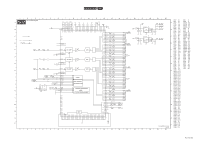

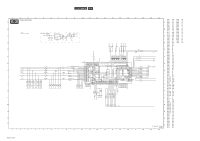

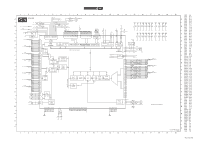

D4 7151 L3EO7040 4 35 GD0-9 44 59 BD0-9 71 109 Uniformity Correction RD0-9 118 HD 124 VD 125 RGB Correction Data 3V3 3 21 DDG0-9 34 45 DDB0-9 58 95 DDR0-9 108 LC3131/LC3141 5-7 Serial Interface 5 6 7 1 SCS SDATA SCLK 3V3 D4 7150 L3EO2090FOA 1 HDDRB 9 Horizontal Count VDDRB 10 Vertical Count Clock generation 7 CKD 2090 Clock Enable generator SCS 14 13 SCLK SDATA 12 Serial interface S/H Clock generation 26645004_037.eps 160402 CLOCK GENERATION 26-60 31 27-61 34 DX (RGB) DY CLX (RGB) CLY 22-56 23-57 ENBX1 (RGB) ENBX2 (RGB) 18-52 19-53 21-55 20-54 SHCLK (RGB) XFR (RGB) STSOO (RGB) STSOE (RGB) 15 Reset 6 26645004_038.eps 160402 PCS 107 372 5-8 LC3131/LC3141 D5-6-7 7250 L3EO6060 2 DDDRDG0-09-9 11 FRPR 14 Inverter 15 30 STS00 RLR SHCLKR XFRR RRL 44 42 43 12 13 Timing gen SH1 DAC SH2 DAC SH3 DAC SH4 DAC SH5 DAC SH6 DAC +15V SUBSAMPLING 24 16 +3V3 33 RVID 1 31 RVID 3 29 RVID 5 27 RVID 7 25 RVID 9 23 RVID 11 7260 L3EO6060 (only XGA) FRPR 14 2 11 Inverter +15V +3V3 To the LCD 24 16 SH1 DAC 33 RVID 2 SH2 DAC 31 RVID 4 SH3 DAC 29 RVID 6 SH4 DAC 27 RVID 8 SH5 DAC 25 RVID 10 SH6 DAC 23 RVID 12 Timing gen 15 30 44 42 43 12 13 SHCLKR XFRR STSOE RRL 26645004_039.eps 160402 PCS 107 373 D5-6-7 7251 ET1030F NRSHR 2 NRSLRGB 21 FRPR 19 DYOUT 10 CLYOUT 9 UD 5 DXOUT 8 CLXOUTR 7 ENBX1R 17 ENBX2R 16 NRG 11 +5 +15 1 24 NRS level shifter Clock level shifter & Inverter 12 23 LEVEL SHIFTING 7252-7256 22 NRS1RR 7253-7257 NRS2RR 43 RDY 41 RCLY 42 RCLYN 26 RDX 33 RCLX 34 RCLXN 35 RENBX1 29 RENBX2 30 RNRG 40 RDIRX 27 To the LCD 16645004_040.eps 160402