Sharp XE-A203 Service Manual - Page 17

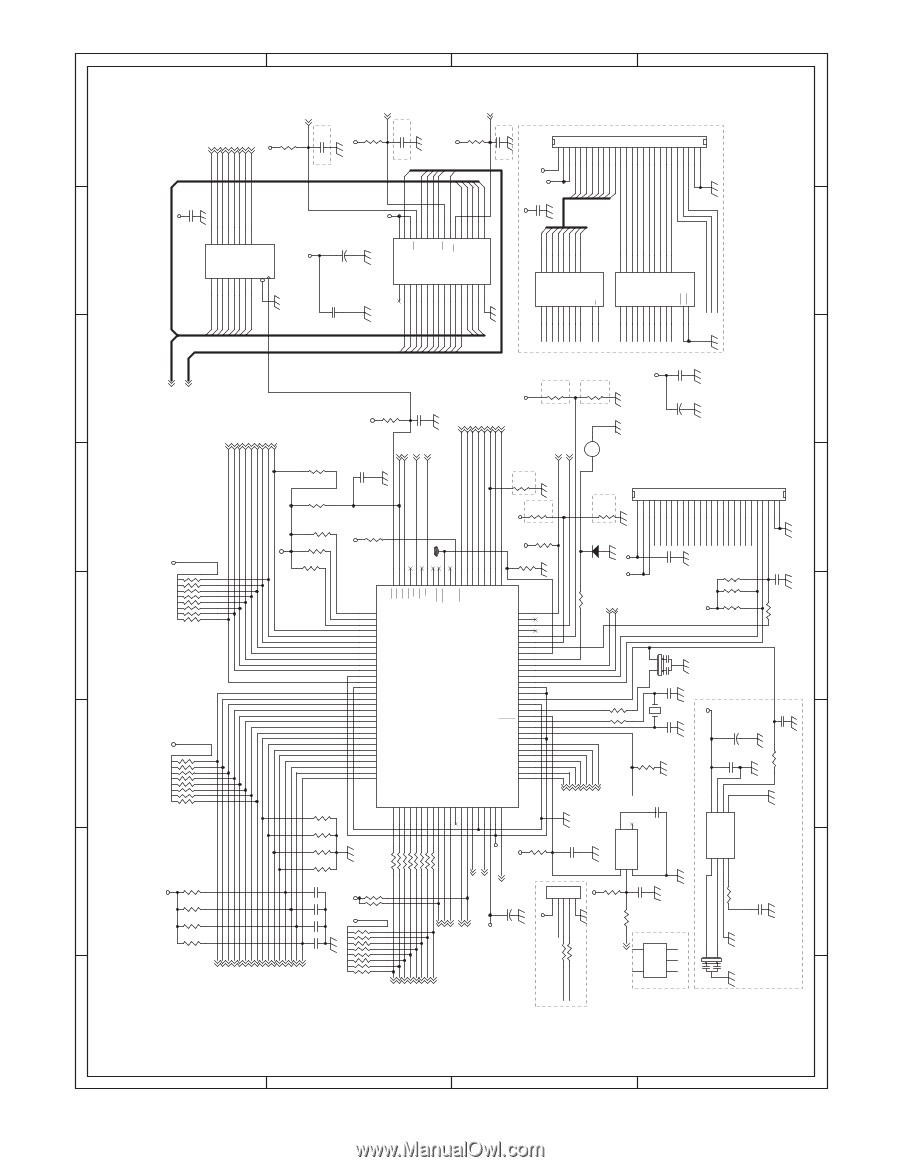

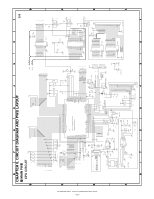

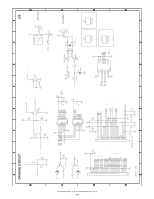

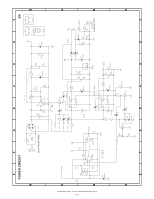

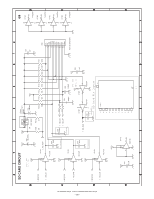

Circuit Diagram And Pwb Layout - cd

|

UPC - 074000049178

View all Sharp XE-A203 manuals

Add to My Manuals

Save this manual to your list of manuals |

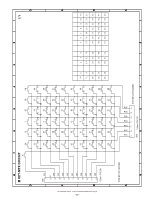

Page 17 highlights

8 7 6 5 4 3 2 1 CHAPTER 6. CIRCUIT DIAGRAM AND PWB LAYOUT ■ MAIN PWB 1/4 XE-A203U/XE-A203A CIRCUIT DIAGRAM AND PWB LAYOUT - 15 - CPU CIRCUIT VCC D R1 R2 R3 R4 VCC RP2 10K 6 7 8 9 10K 10K 10K 10K A7 A6 A5 A4 A3 A2 A1 A0 2 ENA1 2 ENA2 2 IN1 2 IN2 2 KST3 2 KST2 2 KST1 2 KST0 C1 C2 C3 C4 R25 R26 R27 R28 100pF*4(C10-C13) 10K 10K 10K 10K 5 4 3 2 1 9 8 7 6 5 4 VCC RP3 10K VCC 3 2 1 D[0..7] D[0..7] VCC D A[0..16] A[0..16] C5 0.1uF IC1 A8 A9 A10 A11 A12 D0 D1 D2 D3 D4 D5 D6 D7 3 4 7 8 D0 D1 D2 D3 13 14 17 18 D4 D5 D6 D7 Q0 Q1 Q2 Q3 2 5 6 9 Q4 Q5 Q6 Q7 12 15 16 19 a b c d e f g dp a b c d e f g dp 2 2 2 2 2 2 2 2 A13 A14 A15 1 11 OC CLK VCC:20pin GND:10pin VCC A16 74HC374 R12 10K R5 R24 R23 10K 10K 10K R22 R21 10K 10K VDD 1 C6 0.1uF C7 + /WR C9 33pF NOT INSTALL RP1 VCC VCC 10K C R37 R38 VCC R16 C11 33pF VCC 2 10uF/50V VCC C R13 80 79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52 51 9 8 7 6 5 4 3 2 1 10K 10K 10K D8 D9 D10 D11 D12 D13 D14 D15 A0 A1 A2 A3 A4 A5 A6 A7 VSS A8 VCC A9 A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 D7 D6 D5 D4 D3 D2 D1 D0 2 /STB1 2 /LAT 3 VPON R41 33 R43 33 R44 33 R45 33 R46 33 R47 33 R48 33 R49 33 81 82 83 D7 D6 D5 84 85 86 87 D4 D3 D2 D1 88 89 90 91 D0 AN7 AN6 AN5 IC2 FLASH M30626FHPFP 1006P6S-A MASK M30624MWP-XXXFP 3 VBAT 2 /STB2 2 P101 92 93 94 95 AN4 AN3 AN2 AN1 2 VCC 2 1 P100 P97 VDD 96 97 98 99 100 AVSS AN0 VREF AVCC SIN4 + C10 CS0 CS1 CS2 50 49 48 CS3 WR BHE RD 47 46 45 44 CBCLK HLDA HOLD ALE 43 42 41 40 CLKOUT RTS0 CLK0 RXD0 39 38 37 36 TXD0 CLKS1 CLK1 RXD1 TXD1 35 34 33 32 31 10K TP1 /CS0 /CS1 /CS2 /WR /RD R17 10k C8 33pF SD_CLK SD_RXD SD_TXD /SD_POWER /SD_CS /SD_CD /SD_WP DR1 2 SD_CLK 4 SD_RXD 4 SD_TXD 4 /SD_POW 4 /SD_CS 4 /SD_CD 4 /SD_WP 4 VDD /RD IC3 A16 A14 A12 A7 A6 A5 A4 A3 A2 A1 A0 D0 D1 D2 1 2 NC A16 3 4 5 6 A14 A12 A7 A6 7 8 9 10 A5 A4 A3 A2 11 12 13 14 A1 A0 I/O0 I/O1 15 16 I/O2 VSS VCC A15 32 31 CS2 WE A13 A8 30 29 28 27 A9 A11 OE A10 26 25 24 23 CS1 I/O7 I/O6 I/O5 22 21 20 19 I/O4 I/O3 18 17 C12 A15 33pF NOT INSTALL A13 A8 A9 A11 A10 VDD D7 D6 D5 R14 D4 10K D3 LP621024DM-70MM/ CY62128BLL-70SXC SOIC C18 /CS2 NOT INSTALL 33pF SOUT4 CLK4 TB4IN TB3IN SOUT3 SIN3 CLK3 BYTE CNVSS XCIN XCOUT RESET XOUT VSS XIN VCC NMI INT2 INT1 INT0 TA4IN/U TA4OUT/U TB3IN TBEOUT TA2INW TA2OUTW TA1IN/V TA1OUT/V TB5IN TB5OUT 2 4.7UF/50V VDD VCC R39 R51 VCC VCC VCC Not Install 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 R53 47K R15 R42 10K Not Install IC6 C19 VCC CN3 B ONLY QA0/QA1 USE /SD_CD R64 /SD_WP R65 CNVss 0 RXDPRG 0 TXDPRG TEST PIN 100K 5 4 3 2 C13 2 P96 2 P95 1 1000pF 2 2 P94 P93 VDD 2 P92 2 P91 2 P90 R58 1K /RESUSB 2 10K 10K R50 R42 XE-A20W ONLY DAT 2 10K CLK 2 D1 R40 B +BZ1 R52 PIEZO BZ 10K D0 D1 D2 D3 D4 D5 D6 D7 2 3 4 5 A0 A1 A2 A3 6 7 8 9 A4 A5 A6 A7 /RD /CS1 1 19 DIR G B0 B1 B2 B3 18 17 16 15 B4 B5 B6 B7 14 13 12 11 BD0 BD1 BD2 BD3 BD4 BD5 BD6 BD7 74ALS645 VCC3 0.1uF VCC CN2 BD[0..7] 1 2 3 BD0 4 BD1 5 BD2 6 BD3 7 BD4 8 BD5 9 B 2 /RESET 54 123 BD5228 R56 3.3K R57 820 C14 100pF Reset IC IC4 1 2 OUT VDD 3 VSS CD 5 4 NC BD5228/ S80928 rohm SII C15 2200pF CNVss R62 R61 R60 47K C20 18pF 0 330 X2 1 2 C21 27pF 32.768KHz 1 2 3 /DREQUSB /INTUSB X3 MOTOR /POFF 2 3 VCC 1 1SS133 VCC3 D0 D1 C24 D2 D3 D4 0.1uF D5 D6 D7 10K R40 XE-A203U/A ONLY 1 2 3 4 5 6 7 8 9 10 11 2 1 VDD + C17 C16 0.1uF IC7 A0 2 A1 3 A2 4 A3 5 A4 6 A5 7 A6 8 /CS1 9 /WR 10 /RD 11 1 13 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 OE1 OE2 Y1 Y2 23 22 Y3 Y4 Y5 Y6 Y7 Y8 Y9 Y10 21 20 19 18 17 16 15 14 BA0 BA1 BA2 BA3 BA4 BA5 BA6 /CS1B /WR_B /RD_B 74ABT827 BD6 10 BD7 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 X1 CSTLF12M A0 12 26 A 3 2 1 R63 3.3K IC5 1 XIN 2 3 4 XOUT S1 LF VDD 8 S0 FSOUT VSS 7 6 5 FS781 C22 0.1uF 1 VCC Not Install C23 + 10uF/10V,OS VCC R18 R19 R20 10K 10K 10K A1 13 A2 14 A3 15 A4 16 A5 17 A6 18 /CS1 19 /WR 20 10uF/50V,AL /DREQUSB /INTUSB /RESUSB_B 1.0-11-26P A CST12.0MTW 2 /RD 21 C25 /DREQUSB 22 330pF R66 /INTUSB 23 /RESUSB_B 24 25 R70 0 C27 26 C26 33 91pF 1000pF CN1 52806-2610 TO USB 8 7 6 5 4 3 2 1