ASRock G41M-S3 User Manual - Page 32

Overclock Mode, CPU Frequency MHz, PCIE Frequency MHz, Boot Failure Guard, Spread Spectrum, Ratio

|

View all ASRock G41M-S3 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 32 highlights

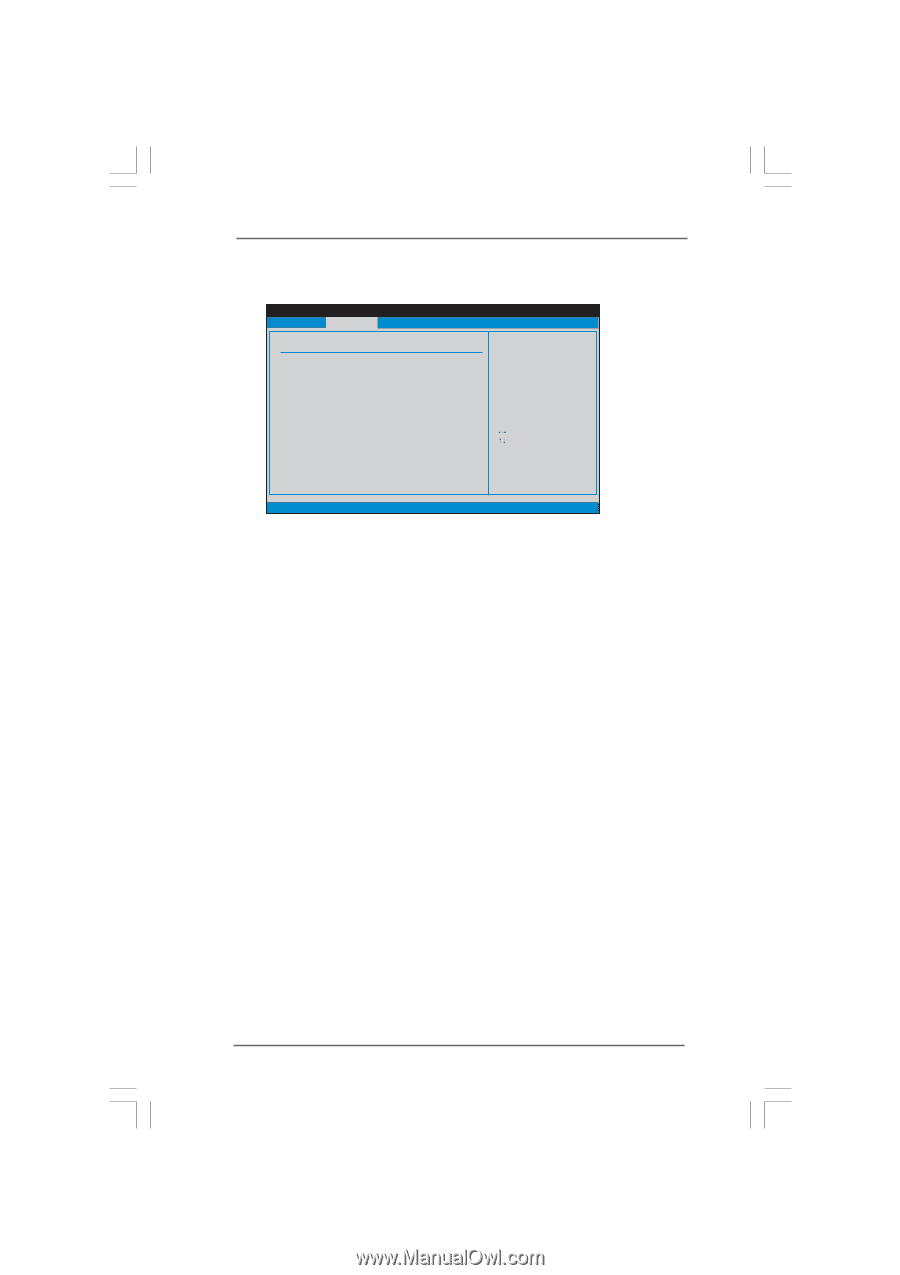

3.4.1 CPU Configuration BIOS SETUP UTILITY Advanced CPU Configuration Overclock Mode CPU Frequency (MHz) PCIE Frequency (MHz) Boot Failure Guard Spread Spectrum [Auto] [200] [100] [Enabled] [Auto] Ratio Status Ratio CMOS Setting Unlocked (Min:06, Max:17) 17 [17] Enhanced Halt State Intel (R) Virtualization tech. CPU Thermal Throttling No-Execute Memory Protection Intel (R) SpeedStep (tm) tech. On-Demand Clock Mudulation [Disabled] [Enabled] [Enabled] [Disabled] [Disabled] [Auto] This should be enabled in order to enable or disable the "Enhanced Halt State". +F1 F9 F10 ESC Select Screen Select Item Change Option General Help Load Defaults Save and Exit Exit v02.54 (C) Copyright 1985-2005, American Megatrends, Inc. Overclock Mode Use this to select Overclock Mode. The default value is [Auto]. Cnfiguration options: [Auto], [Manual] and [Optimized]. CPU Frequency (MHz) Use this option to adjust CPU frequency. PCIE Frequency (MHz) Use this option to adjust PCIE frequency. Boot Failure Guard Enable or disable the feature of Boot Failure Guard. Spread Spectrum This item should always be [Auto] for better system stability. Ratio Status This is a read-only item, which displays whether the ratio status of this motherboard is "Locked" or "Unlocked". If it shows "Unlocked", you will find an item Ratio CMOS Setting appears to allow you changing the ratio value of this motherboard. Ratio CMOS Setting If the ratio status is unlocked, you will find this item appear to allow you changing the ratio value of this motherboard. If the CPU you adopt supports EIST (Intel (R) SpeedStep(tm) tech.), and you plan to adjust the ratio value, please disable the option " Intel (R) SpeedStep(tm) tech." in advance. Enhance Halt State All processors support the Halt State (C1). The C1 state is supported through the native processor instructions HLT and MWAIT and requires no hardware support from the chipset. In the C1 power state, the processor maintains the context of the system caches. 32