HP ProLiant BL660c AMD Opteron™ and Intel® Xeon® x - Page 10

Power management

|

View all HP ProLiant BL660c manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 10 highlights

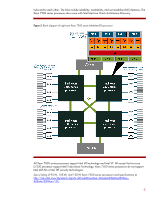

Intel QuickPath Technology The QuickPath Interconnect (QPI) transmits data packets in parallel across two 20-bit links. Each link uses up to 16 bits (2 bytes) to transfer data and 4 bits for protocol and error correction. The QPI performs a maximum of 6.4 GT/s with 2 bytes per transfer, or 12.8 GB/s in each direction for a total theoretical bandwidth of 25.6 GB/s. The QPI's Reliability, Availability, and Serviceability (RAS) features include self-healing links and clock failover. Each 20-bit link divides into quadrants with five lanes each. As shown in Figure 5, if a persistent (hard) error occurs in one quadrant, the link automatically reduces its width to half (two quadrants) or quarter-width (one quadrant) using only the good lanes. This self-healing capability allows the interconnect to recover from multiple hard errors without data loss. Unrecoverable soft errors initiate a process to reduce the dynamic link width. If the clock fails, the link reduces to half- or quarter-width, and the clock maps to a pre-determined data lane. The bandwidth of the link in RAS mode decreases, but the link in the other direction operates as usual. Figure 5. Normal operation of QPI uni-directional link (top). A hard error reduces link bandwidth (bottom). Power management AMD and Intel multi-core processors contain power management features that maximize performanceper-watt and improve energy efficiency. Intel Xeon power management QuickPath Interconnect power The Xeon 5500 and 5600 series processors let QPI buffers enter a sleep state to reduce power requirements of inactive QPI links. ProLiant G6 and G7 servers enable this feature by default. You can change it through the HP ROM-Based Setup Utility (RBSU). The Xeon processor determines when to put the QPI links into a low power state with minimal performance impact. 10