HP ProLiant BL660c AMD Opteron™ and Intel® Xeon® x - Page 7

Instruction set architecture

|

View all HP ProLiant BL660c manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 7 highlights

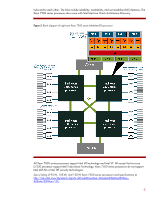

The AMD Opteron processor uses the following technologies: HyperTransport (HT) Assist, also called a probe filter, increases performance of AMD Opteron processor-based systems with four or eight sockets. It maintains data correctness, or coherence, between the processors and minimizes inter-processor communication traffic on the HyperTransport links. AMD Smart Fetch Technology lets cores enter a "halt" state during idle processing times, allowing them to draw less power. Data moves from the L1 and L2 caches to the shared L3 cache before going into the halt state. This allows the system to retrieve the contents of the idle cores. Enhanced AMD PowerNow! delivers optimum performance-per-watt and power savings. AMD-P suite of power-management features helps reduce energy use and cost (see "Power management"). AMD-V™ with Rapid Virtualization Indexing reduces software virtualization overhead. (See "Virtualization"). Instruction set architecture AMD Opteron and Intel Xeon processors adhere to the x86 instruction set architecture and are compatible with most 32-bit software applications. The x86-instruction set includes all instructions in the original 16-bit 8086 processor and enhanced instructions in succeeding x86 processors. 32-bit operations A 32-bit processor has general-purpose registers (GPRs) 32 bits wide. The 32-bit processor can operate on an integer data stream that is 32 bits wide. The processor can also hold 32 bits of memory address data in a single register, for a maximum of 4 GB of addressable memory. The x86 architecture supports physical addressing extensions (PAE) that expand the address space to allow addressing to 36 bits. This gives a maximum of 64 GB of physical addressable memory. AMD Opteron and Xeon processors support 32-bit addressing and the 36-bit PAE. As shown in Table 3, the 32-bit instruction set for both the Xeon and AMD Opteron family processors includes: Standard x86 instructions that are general-purpose arithmetic functions Single Input Multiple Data (SIMD) Instructions that let one command work simultaneously on multiple data items. This includes Streaming SIMD Extensions (SSE), SSE2, SSE3, and SSE4a instructions. x87 floating point instructions 7