HP ProLiant BL660c AMD Opteron™ and Intel® Xeon® x - Page 9

AMD HyperTransport 3.0 technology

|

View all HP ProLiant BL660c manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 9 highlights

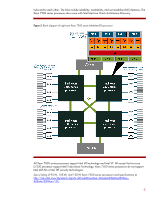

AMD HyperTransport 3.0 technology The HT3 interconnect consists of two uni-directional links. Each 16-bit (2-byte) link performs two data transfers per clock cycle (double-pumped) with a maximum transfer rate of 6.4 gigatransfers per second (GT/s). This gives each uni-directional link a maximum data rate of 6.4 GT/s × 2 bytes per transfer, or 12.8 GB/s. The four HT3 links improve performance in 4P systems because the processors can communicate directly rather than moving data from one processor to another. The AMD64 architecture uses a Non-Uniform Memory Access (NUMA) design to improve performance with multi-threaded applications. The NUMA design gives each AMD Opteron processor a local memory pool and then connects it to similar processors with their own memory pools. This design lets each processor access non-local memory. But access time varies based on memory pool location. HT3 links can be coherent (cHT) or non-coherent (ncHT). Coherent links transfer cache coherency data. They connect two or more AMD Opteron processors and their memory pools. Non-coherent links move data between memory and I/O devices. (See Figure 4). Figure 4. Coherent HT3 links connect processors, and non-coherent HT3 links move data from memory to I/O devices. 9