HP ProLiant DL380p DDR3 memory technology - Page 5

Symmetrical T-Branch Topology

|

View all HP ProLiant DL380p manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 5 highlights

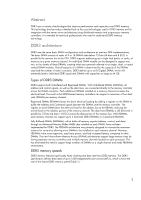

ensure that command and address signals arrive at all the DRAMs as close to simultaneously as possible. With this design, all of the DRAMs present their data (during a read) to the memory bus at the same time. The set of parallel bits is then read by the memory controller. The window of time in which the data bits are available to be read is known as the data-eye, and as memory clock speeds have increased, this window has become increasingly small. Figure 2. DDR2 and DDR3 address/command signal topologies DDR2 Symmetrical T-Branch Topology Data Data Address / Command / Clock Bus Memory Controller DDR3 Fly-by Topology Data Data Address / Command / Clock Bus Memory Controller Fly-by topology solves the problem of the shrinking data-eye by eliminating the need to simultaneously deliver the data signals to each DRAM. With Fly-by topology, each command and address signal is routed along a single path that goes from DRAM 0 to DRAM 8. This simpler topology helps increase signal integrity. However, it guarantees that the command and address signals will not arrive at each 5