LG KE600 Service Manual - Page 64

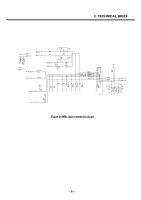

Transmitter part block diagram

|

View all LG KE600 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 64 highlights

3. TECHNICAL BRIEF The digital transmitter architecture is based on a polar modulation architecture, where the analog modulation data (rectangular I/Q coordinates) is converted to digital data stream and is subsequently transformed to polar coordinates by means of a CORDIC algorithm. The resulting amplitude information is fed into a digital multiplier for power ramping and level control. The ready processed amplitude signal is applied to a DAC followed by a low pass filter which reconstructs the analog amplitude information. The phase signal from the CORDIC is applied to the Sigma-Delta fractional-N modulation loop. The divided output of its associated VCO is fed to a highly linear amplitude modulator, recombining amplitude and phase information. The output of the amplitude modulator is connected to a single ended output RF PGA for digitally setting the wanted transmit power. The PA interface of SMARTi-PM supports direct control of standard dual mode power amplifiers (PA's) which usually have a power control input VAPC and an optional bias control pin VBIAS for efficiency enhancement. In GMSK mode, the PA is in saturated high efficiency mode and is controlled via its VAPC pin directly by the baseband ramping DAC. In this way both up- / down-ramping and output power level are set. In 8PSK mode, the ramping functionality is assured by an on-chip ramping generator, whereas output power is controlled by the PGA's as described above. Figure 38 Transmitter part block diagram - 65 -