LG KE990 Service Manual - Page 28

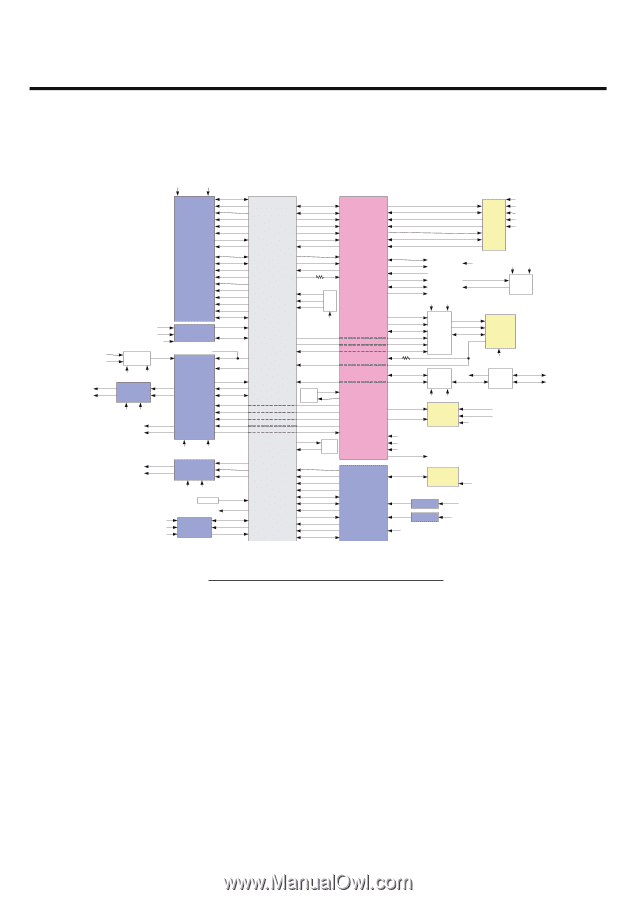

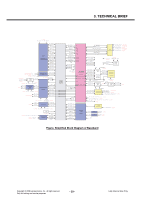

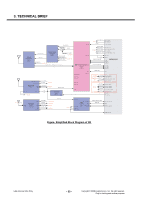

Simplified Block Diagram of Baseband

|

View all LG KE990 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 28 highlights

3. TECHNICAL BRIEF From PMIC VREG_ MSMP_ 2. 7V VREG_ MSME_1.8V EBI2 _ DATA[ 0: 15] NAND_ CS_N NAND_ ALE NAND_ CLE EBI2 _OE_N EBI2 _WE_N NAND_ READY RESOUT_ N MCP SDRAM_ DATA[ 0: 31] TOSHIB A 2G/1G TYA000BC00HOGG SDRAM_ ADDR [0:12] SDRAM_ DQM[0:3 ] SDRAM_CLK SDRAM_ CS_ N SDRAM_ RAS_N SDRAM_ CAS_N SDRAM_WE_N SDRAM_ CLK_ EN SDRAM_ ADDR[ 13: 14] X +/From TOUCH WINDOW Y +/- From LDO LCD_ VDD_2. 8V From CAM_ MIC CAM_ MIC+ EAR_ MIC_P From MMI An alog S/W NC7 SB 3157 MIDI_ MICP From ESM From PMIC VREG_ MSMP_2 .7 V EAR_ SENSE _N To MMI MIDI_ EAR_L MIDI_ EAR_R Headphone AMP MAX 9722 BETE HP_ EAR_L HP_ EAR_R From LDO MIDI_3.3V HP_ AMP_ EN From ESM To MODULE SPEAKER SPK _ OUT+ SPK _ OUT- Touch D river TSC2007IYZGR TOUCH_ PENIRQ_N TOUCH_I2C _ SDA/SCL From FM RADIO FM_ AUDIO_R /L SPK_ R /L AUDIO CODEC WM8983 HP_R /L MIC2 P CODEC_I2 C_ SCL CODEC_I2C _ SDA MMP_A _ BCLK MMP_A_ LRCLK MMP_ADI_ DACDAT MMP_A_ MCLK MMP_ADI_ ADCDAT To MOTOR From LDO MOTOR+ MOTOR- MIDI_3 .3V VREG_ 5V VREG_WM_ 2.7 V From PMIC VREG_ MSME_1.8V LIN_ PWM_ MAG Li near Motor Dri ver LIN_ INVETER LIN_ PWM_ FREQ From PMIC VREG_ MMC_3 .0V LIN_ MOTOR_EN From ESM From PMIC VREG_ MSMP_ 2.7 V / VREG_ MMC_3 .0V From PMIC SLEEP_ CLK From MMI FM_ ANT MIC To RECEIVER MIC1P /1N RCV+/- FM RADIO TEA 5766UK I2C _ SCL/ SDA FM_ BUSEN FM_ INTX ESM 6270 EBI2_ DATA[ 0: 15] EBI2_ ADDR [11: 13] MMP_ CS_N NAND_ ALE EBI2 _OE_N EBI2 _WE_N MMP_ INT_N MMP_ HPCM_CLK MMP_ HPCM_ FSYNC MMP_ HPCM_DO MMP_ HPCM_DI NA HD HA HCS0 N HCS1 N HRDN HWRN HGINTN HPCMCLK HPCMFS HPCMDO HPCMDI CAM_ MODE3 _N CAM_ MODE2 _N CAM_ MODE1 _N MODE S /W VREG_ MSMP_2 .7 V From PMIC ZORAN ZR3453 27 M Cr ys tal MMP_XTAL_IN MMP_ XTAL_ OUT USB_ XTAL _ IN USB_ XTAL_ OUT 48 M Crystal VREG_ MSMC_ 1.2V VREG_ MSME_1.8V VREG_ MSMP_2.7V VREG_ MSMA_ 2.6V USIM_ DATA/CLK/RST_N SSBDT_ PM RESET _IN_ N PS_ HOLD PM_INT _ N SLEEP_ CLK USB_OE_EN/DAT / SEO PMIC PM6635 MMP_ CAM_ MCLK MMP_ CAM_ DATA[ 0: 7] MMP_ CAM_ VSYNC/ HSYNC MMP_ CAM_ PCLK MMP_ CAM_ RESET_N MMP_I 2C_ SDA/ SCL MMP_ CAM_INT 5M Camera CAM_ VDD_ CORE_1 .2 V From DCDC CAM_ VDD_ AF_2. 7V From LDO( SUB) CAM_ VDD_ SA_2.7 V From LDO CAM_ VDD_ SD_1.8V From LDO( SUB) CAM_ VDD_ IO_ 2.7 V From LDO MMP_LCD_ DATA[0:15] LCD_ IF_ MODE LCD_ MAKER_ID LCD_ RESET_N MMP_LCD_ VSYNC I/O MMP_ LCD_CS /RD/ WE/ ADS LCD_ VDD_2 .8 V From LDO From ESM LCD_BL _ CTRL VPWR WLED[1: 5] WLED_ PWR Charge Pump AAT 3169 IFO VPWR MMC_ SELECT_N From ESM MMP_ MICROSD_ CLK MMP_ MICROSD_ CMD MMP_ MICROSD_ DATA[ 0: 3] An alog S/W MSM_ MICROSD_ CLK MSM_ MICROSD_ CMD MSM_ MICROSD_ DATA[ 0: 3] MAX 4701ETE ( DATA LINE) SL AS 4717 EP (CLK / CMD ) MICROSD_ CL K MICROSD_ CMD MICROSD_ DATA[ 0: 3] MicroSD Connector SCHA1B 0102 NA MICROSD_ DET_N MMP_ USB_ D+/MSM_ USB_D+/- An alog S/W FSUSB30 UMX VREG_ MMC_3 .0V From PMIC To ESM RMT_ INT/ RMT_ ADC USB_D +/- An alog S/W FSUSB30 UMX RMT_ INT- USB_D+ RMT_ADC- USB_ D- To MMI VPWR USB_ SELECT_N MMP_ STROBE_ READY MMP_ STROBE_ CHARGE Strobe F lash Connector STROBE_ TRIGGER FLSH_ DRV_N From 5 M CAMERA From PMIC VREG_ MSMP_2.7V / VREG_ 5V / VPWR From PMIC MMP_ VDD_ CORE_1 .0V / CAM_ VDD_ IO_ 2.7 V From LDO LCD_ VDD_2.8V / MMP_ VDD_1 .9 V From LDO VREG_ MSMP_ 2.7V/ VREG_ MMC_3 .0V / VREG_ USB_3.0V / VREG_5V From PMIC TV _ OUT To MMI USIM_P _ DATA/ CLK/RST_N SIM Connector VREG_ USIM_ 3.0 V From PMIC USB_ VBUS OVP NUS 3065 MUTAG USB_ VBUS From MMI +5 V_ PWR OVP NUS 3065 MUTAG + 5V _ PWR From MMI VPWR Figure. Simplified Block Diagram of Baseband Copyright © 2008 LG Electronics. Inc. All right reserved. Only for training and service purposes - 29 - LGE Internal Use Only