LG KE990 Service Manual - Page 42

External memory interface

|

View all LG KE990 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 42 highlights

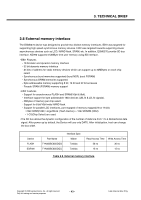

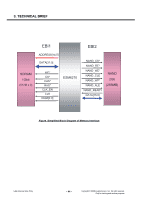

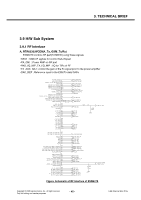

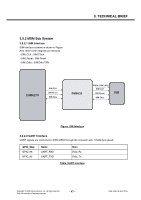

3. TECHNICAL BRIEF 3.8 External memory interface The ESM6270 device was designed to provide two distinct memory interfaces. EBI1 was targeted for supporting high speed synchronous memory devices. EBI2 was targeted towards supporting slower asynchronous devices such as LCD, NAND flash, SRAM, etc. In addition, ESM6270 provide SD bus interface. KE990 supports 512MByte free user memory using SD interface. • EBI1 Features - 16 bit static and dynamic memory interface - 32 bit dynamic memory interface - 24 bits of address for static memory devices which can support up to 32MBytes on each chip select - Synchronous burst memories supported (burst NOR, burst PSRAM) - Synchronous DRAM memories supported - Byte addressable memory supporting 8 bit, 16 bit and 32 bit accesses - Pseudo SRAM (PSRAM) memory support • EBI2 Features - Support for asynchronous FLASH and SRAM(16bit & 8bit). - Interface support for byte addressable 16bit devices (UB_N & LB_N signals). - 2Mbytes of memory per chip select. - Support for 8 bit/16bit wide NAND flash. - Support for parallel LCD interfaces, port mapped of memory mapped(18 or 16 bit). • 2Gb NAND(16bit, Large Block ) flash memory + 1Gb SDRAM (32bit) • 1-CS(Chip Select) are used. • The SD bus allows the dynamic configuration of the number of data line from 1 to 4 Bidirectional data signal. After power up by default, the Device will use only DAT0. After initialization, host can change the bus width. Device FLASH SDRAM Part Name TYA000BC00DOGG TYA000BC00DOGG Interface Spec Maker Toshiba Toshiba Read Access Time 50 ns 15 ns Write Access Time 30 ns 15 ns Table 3.8. External memory interface Copyright © 2008 LG Electronics. Inc. All right reserved. Only for training and service purposes - 43 - LGE Internal Use Only