LG KE990 Service Manual - Page 52

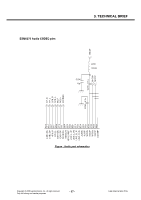

Pin Description ] - master reset

|

View all LG KE990 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 52 highlights

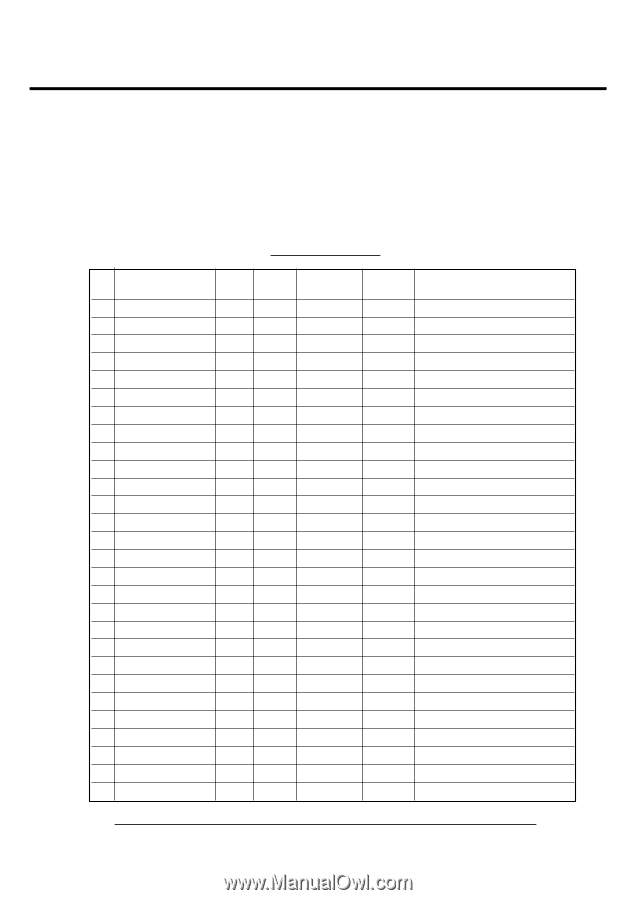

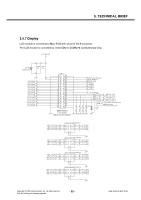

3. TECHNICAL BRIEF The MEGA Camera module is connected to Main PCB with 30pin Board to Board connector Its interface is dedicated camera interface port in Multimedia chip. The camera port supply 13MHz master clock to camera module, vertical sync signal, horizontal sync signal, reset signal and 8bits data from camera module. The camera module is controlled by I2C port from Multimedia chip. [ Pin Description ] No Symbol 1 AF_GND 2 GND 3 VDD_AF(2.8V) 4 SCL 5 GND 6 SDA 7 VDD_SA(2.8V) 8 VSYNC 9 VDD_IO(2.8or1.8V) 10 HSYNC 11 TRIG 12 XRST 13 GND 14 STRB 15 D[7] 16 D[6] 17 D[5] 18 D[4] 19 D[3] 20 D[2] 21 D[1] 22 D[0] 23 VDD_SD(1.8V) 24 GND 25 DCK 26 MCK 27 GND 28 VDD_L(1.2V) I/O State at State at State at reset power save power off - - - - - - - - - - - - I/O HiZ Active HiZ - - - - I/O HiZ Active HiZ - - - - O Low HiZ HiZ - - - - O Low HiZ HiZ O Low Low Low I - - - - - - - O Low Low Low O Low HiZ HiZ O Low HiZ HiZ O Low HiZ HiZ O Low HiZ HiZ O Low HiZ HiZ O Low HiZ HiZ O Low HiZ HiZ O Low HiZ HiZ - - - - - - - - O Low HiZ HiZ I - - - - - - - - - - - Description Ground(Auto Focus) Ground Voltage Supply(Auto Focus) I2C Serial Bus Clock Ground I2C Serial Bus Data I/O Voltage Supply(Sensor Analog) Vertical Synchronization Signal Voltage Supply(I/O) Horizontal Synchronization Signal Interrupt Line Signal System Reset Ground LED/Xenon Strobe Contol Digital Video Data(MSB) Digital Video Data Digital Video Data Digital Video Data Digital Video Data Digital Video Data Digital Video Data Digital Video Data(LSB) Voltage Supply(Sensor Digital) Ground Digital Video Data Clock System Clock Input Ground Voltage Supply(DSP Core) Table. Interface between MEGA Camera Module and MAIN PCB (in camera module) Copyright © 2008 LG Electronics. Inc. All right reserved. Only for training and service purposes - 53 - LGE Internal Use Only