LG KG270 Service Manual - Page 33

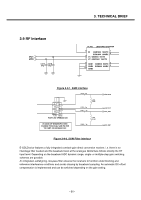

Signals, Description

|

View all LG KG270 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 33 highlights

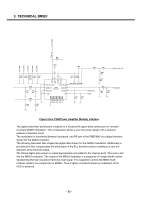

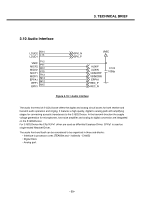

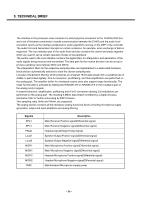

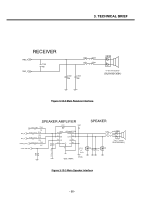

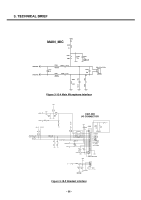

3. TECHNICAL BRIEF The interface to the processor cores consists of a direct physical connection to the TEAKlite DSP bus and a set of firmware commands to handle communication between the C166S and the audio frontend which serves as the interface peripheral for audio algorithms running on the DSP or the controller. The audio front-end Generates interrupts on certain occasions, for example, when exchange of data is requested. The core interface part of the audio front-end also contains the control and status registers which are used to set up certain operation modes of the peripheral. The section next to the core interface contains the digital filters for interpolation and decimation of the audio signals being received and transmitted. The data path for the receive direction can be set up to process sampling rates between 8kHz and 48kHz. The interpolation filters for the respective sampling rates are implemented in a dedi-cated hardware block and are automatically selected to suite the chosen sampling rate. Low-pass interpolation filtering, which produces an unsigned 16-bit data stream with a sampling rate of 4 MHz, is performed digitally. D-to-A conversion, postfiltering, and final amplification are performed on the analog part. The amplifier buffer for voiceband receive does also support ringer functionality. The ringer functionality is activated by Setting bits RINGSELPN or RINGSELPA in the voiceband part of the analog control register. In transmit direction, amplification, prefiltering and A-to-D conversion (analog ∑∆ modulation) are performed on the analog part. The resulting 2-Mbit/s data stream is filtered by a digital low-pass decimation filter for further processing by DSP firmware. Two sampling rates, 8kHz and 16kHz, are supported. The analog section contains all the necessary analog functional blocks including microphone supply generation, output and input amplifiers and analog filtering. Signals EPp1 EPn1 EPpa1 Loud1 Loud2 MICP1 MICN1 MICP2 MICN2 VMIC Description Main Receiver Positive signal(Differential signal) Main Receiver Negative signal(Differential signal) Headset signal(Single Ended signal) Speaker Output Positive signal(Differential signal) Speaker Output Negative signal(Differential signal) Main Microphone Positive signal(Differential signal) Main Microphone Negative signal(Differential signal) Headset Microphone Positive signal(Differential signal) Headset Microphone Negative signal(Differential signal) Main/Headset Microphone supply power - 34 -