LG KG270 Service Manual - Page 42

FM Tunner, 15.2 Headphone Amplifier

|

View all LG KG270 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 42 highlights

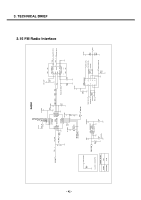

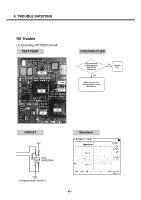

3. TECHNICAL BRIEF 3.15.1 FM Tunner The Si4702 patented digital low-IF architecture reduces external components and eliminates the need for factory adjustments. The receive (RX) section integrates a low noise amplifier (LNA) supporting the worldwide FM broadcast band (76 to 108 MHz). An automatic gain control (AGC) circuit controls the gain of the LNA to optimize sensitivity and rejection of strong interferers. For two-wire operation, a transfer begins with the START condition. The control word is latched internally on rising SCLK edges and is eight bits in length, comprised of a seven bit device address equal to 0010000b and a read/write bit (write = 0 and read = 1). The device acknowledges the address by setting SDIO low on the next falling SCLK edge. For write operations, the device acknowledge Is followed by an eight bit data word latched internally on rising edges of SCLK. The device always acknowledges the data by setting SDIO low on the next falling SCLK edge. An internal address counter automatically increments to allow continuous data byte writes, starting with the upper byte of register 02h, followed by the lower byte of register 02h, and onward until the lower byte of the last register is reached. The internal address counter then automatically wraps around to the upper byte of register 00h and proceeds from there until continuous writes cease. Data transfer ceases with the STOP command. After every STOP Command, The internal address counter is reset. For read operations, the device acknowledge is followed by an eight bit data word shifted out on falling SCLK edges. An internal address counter automatically increments to allow continuous data byte reads, starting with the upper byte of register 0Ah, followed by the lower byte of register 0Ah, and onward until the lower byte of the last register is reached. The internal address counter then automatically wraps around to the upper byte of register 00h and proceeds from there until continuous reads cease. After each byte of data is read, the controller IC should return an acknowledge if an additional byte of data will be requested. Data transfer ceases with the STOP command. After every STOP command, the internal address counter is reset. 3.15.2 Headphone Amplifier The MAX4411 fixed-gain, stereo headphone driver features Maxim's patented DirectDrive architecture, eliminating the large output-coupling capacitors required By conventional single-supply headphone drivers. The device consists of two 80mW Class AB headphone drivers, internal feedback network (fixed -1.5V/V gain), undervoltage lockout (UVLO)/shutdown control, charge pump, and comprehensive click-and-pop suppression circuitry. - 43 -