Pioneer SX-255R Service Manual - Page 20

PDG172A, IC826

|

View all Pioneer SX-255R manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 20 highlights

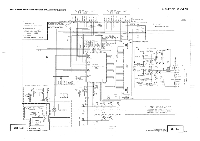

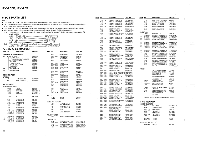

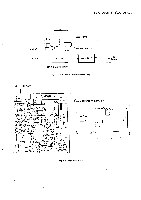

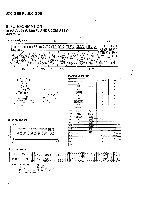

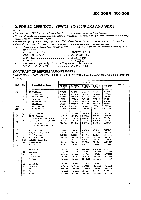

SX-255R, SX-205 8. IC INFORMATION • The information shown in the list is basic information and may not correspond exactly to that shown in the schematic diagrams. • PDG172A (IC826: FL AND UCOM ASSY) • Receiver Control Micro-computer • Block Diagram ANO to ANT I 8 TO to TT , 0 TVS 28 y• 8 115/S 2t SO to 520 t 2I VF DP I cS0 SIO SOO Tea Sit rel ig ECOt: To LrINnT AID CONVERTER FOP CONTROLLER/ DRIVER RAM 80 BYTES R CMOCON Ft FO SERIAL INTERFACE UNIT 0 I FIFO SERIAL INTERFACE UNIT OBIT TIMER/COUNTER 0 8 INT TIMER 1 16611 CAPTURE TIMER / CCONTER 2 INTERRUPT CONTROLLER rr-T tato180104T2 :NTS EXTAt. XFAL. RST Imo tat SPITED CPU CORE ROM 16X BYTES PRESCALER / TIME SASE TIMER CLOCK GEN./ a PAO to PA7 SYSTEM CONTROL RAM 624 BYTES c> 0 r7ta - PEIO to POD 1 , Par • B PCO to PC7 o I POO to PD7 --to i PEO to PA PER to PE7 8 PPP to PF7 - C> g (.. 1P°3 to PO3 e Pin Assignment (Top view) k,"-; cf, s FES/11473 PE4/RA1C PE5 PER PET/TO P00/LINT ',C5° P82/SCK0 P63/510 P84/500 PBS/56kt P86/5I1 PB7/501 PCO/KRO PCI/ KR1 PC2/KR 2 PC3/ KR 3 PC4/KR4 PCS/KR5 PC6/806 PCT/KR7 P/10/4140 PP I/PN I PA 2/4112 as 79 TB O 2 3 4 5 6 7 8 9 10 12 IS 14 IS 16 IT IB 19 20 21 23 24 25 26 76 75 72 TI 9 68 66 PDG172A 30 31 33 36 7 313 9 ,•, ' 64 T6 63 TT 62 18/520 6I T9/527 60 7107326 59 711/525 P0712/524 7137523 7147522 55 7157521 54 520 1.3 5:9 sus 51 SIT 516 PF IS 48 • PF6/S14 P13/513 46 • P14/512 45 • PF3/SI I 44 • P12/510 43 PFI/59 4 PF0/58 P07/3T • Pin Function No. Pin Name I/O Description 1 PE3/INT3 I External interrupt request input terminal 2 PE4/RMC I Remote control reception circuit input terminal 3 PE5 I 4 PE6 O 5 PE7/TO O 16 bit timer/counter rectangular wave output terminal 6 PB0/CINT I/O External capture input terminal to the 16bit timer/counter 7 PB1/CSO I/O Serial interface (CH 0) chip select input terminal 8 PB2/SCK0 I/O Serial clock (CH 0) I/O terminal 9 PB3/SI0 I Serial data (CH 0) input terminal 10 PB4/SO0 O Serial data (CH 0) output terminal 11 PB5/SCK1 1/O Serial clock (CH 1)1/O terminal 12 PB6/SI1 I Serial data (CH 1) input terminal 13 PB7/SO1 O Serial data (CH 1) output terminal 28