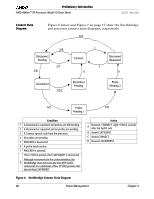

AMD AXDA3200DKV4E Data Sheet - Page 29

Connect, Pending, Processor Connect State Diagram

|

View all AMD AXDA3200DKV4E manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 29 highlights

26237C-May 2003 Preliminary Information AMD Athlon™ XP Processor Model 10 Data Sheet 1 Disconnect Pending 3/A Connect 2/B Disconnect 6/B Connect Pending 2 5 Connect Pending 1 4/C Condition 1 CONNECT is deasserted by the Northbridge (for a previously sent Halt or Stop Grant special cycle). 2 Processor receives a wake-up event and must cancel the disconnect request. 3 Deassert PROCRDY and slow down internal clocks. 4 Processor wake-up event or CONNECT asserted by Northbridge. 5 CLKFWDRST is deasserted by the Northbridge. 6 Forward clocks start three SYSCLK periods after CLKFWDRST is deasserted. Action A CLKFWDRST is asserted by the Northbridge. B Issue a Connect special cycle.* C Return internal clocks to full speed and assert PROCRDY. Note: * The Connect special cycle is only issued after a processor wake-up event (interrupt or STPCLK# deassertion) occurs. If the AMD Athlon™ system bus is connected so the Northbridge can probe the processor, a Connect special cycle is not issued at that time (it is only issued after a subsequent processor wake-up event). Figure 7. Processor Connect State Diagram Chapter 4 Power Management 17