HP rp8440 Site Preparation Guide, Fourth Edition - HP Integrity rx8640, HP 900 - Page 24

System Backplane to Cell Board Connectivity, Clocks and Reset, PCI/PCI-X I/O Subsystem

|

View all HP rp8440 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 24 highlights

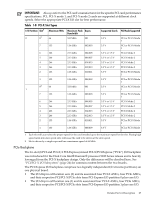

The two LBA PCI bus controllers on the system backplane create the PCI bus for the core I/O cards. You must shut down the partition for the core I/O card before removing the card. Having the SCSI connectors on the system backplane allows replacement of the core I/O card without having to remove cables in the process. System Backplane to Cell Board Connectivity The system backplane provides four sets of connectors, one set for each cell board. The system backplane routes the signals from the cell boards to the communication crossbars. Cell boards 0 and 1 are directly connected to the I/O backplane found in the server. Cell boards 2 and 3 can be connected to a separate I/O expansion chassis connected to the system backplane. System Backplane to Core I/O Card Connectivity The core I/O cards connect at the rear of the system backplane through two connectors. SCSI and LAN on a core I/O are accessed via a PCI-X 66 MHz bus. Two LBA bus controllers located on the system backplane allow communication to the I/O devices. The LBAs are connected to the SBA on the PCI-X backplane by single ropes. The system backplane routes the signals to the various components in the system. The core I/O signals include the SCSI bus for the system hard drives and the bus for the removable media devices. Each core I/O card provides SCSI buses for the mass storage devices. The management processor for the chassis resides on the core I/O card, so the system backplane also provides interfaces required for management of the system. These interfaces and the manageability circuitry run on standby power. You can remove the core I/O cards from the system as long as you shut down the partition for the core I/O card before removing the card. The hot-plug circuitry that enables this feature is located on the system backplane near the core I/O sockets. System Backplane to PCI-X Backplane Connectivity The PCI-X backplane uses two connectors for the SBA link bus and two connectors for the high-speed data signals and the manageability signals. SBA link bus signals are routed through the system backplane to the cell controller on each corresponding cell board. The high-speed data signals are routed from the SBA chips on the PCI-X backplane to the two LBA PCI bus controllers on the system backplane. Clocks and Reset The system backplane contains reset and clock circuitry that propagates through the whole system. The system backplane central clocks drive all major chip set clocks. The system central clock circuitry features redundant, hot-swappable oscillators. PCI/PCI-X I/O Subsystem The cell board to the PCI-X board path runs from the CC to the SBA, from the SBA to the ropes, from the ropes to the LBA, and from the LBA to the PCI slots as shown in Figure 1-12. The CC on cell board 0 and cell board 1 communicates through an SBA over the SBA link. The SBA link consists of both an inbound and an outbound link with a peak bandwidth of approximately 11.5 GB/s at 3.2 GT/s. The SBA converts the SBA link protocol into "ropes." A rope is defined as a high-speed, point-to-point data bus. The SBA can support up to 16 of these high-speed bidirectional rope links for a total aggregate bandwidth of approximately 11.5 GB/s. There are LBA chips on the PCI-X backplane that act as a bus bridge, supporting either one or two ropes for PCI-X 133 MHz slots and the equivalent bandwidth of four ropes for PCI-X 266 slots. Each LBA acts as a bus bridge, supporting one or two ropes and capable of driving 33 MHz or 66 MHz for PCI cards. The LBAs can also drive at 66 MHz or 133 MHz for PCI-X mode 1 cards, 24 HP Integrity rx8640 and HP 9000 rp8440 Server Overview